Weird loopy transistors

Causing Strange (loopy) voltage/current diagrams

- Original observation - Low Avalanche Breakdown Hypothesis - June 2007

- Major surface cleaning experiment - December 16, 2016, from Robert Garner

- Major surface cleaning experiment - December 16, 2016, from Constantin Bulucea

- Human breath on exposed germanium transistor - April 12, 2020, from Robert Garner

- March 1, 2007 update

- Germanium Alloy Transistors, a bit of history by Rick Dill, 2008

- Rick Dill's comments on "Loopy Transistors" - added July 2009

- Bill Newman's tests - PowerPoint, 550 K bytes, added August 4, 2009

- Loopy Transistor frequency response YouTube - Bill Newman

- Lectures on Memristors added Feb 13, 2016

- E-mails to Robert Garner

- Dill to Garner - Re: Alloy Transistors - 09/03/2008

- Newman to Garner - loopy article - 07/05/2009

- Dill to Garner - Re: Science behind loopy transistors - 12/08/2009

- Dill to Garner - Re: Science behind loopy transistors - 12/09/2009

- Meyerson to Garner - Re: Loopy I-V curves in 1950s Ge alloy-junction transistors - 04/23/2014

- Dill to Garner - 03/26/2016

- Dill to Garner - 03/28/2016 - More on Loopy Transistors

- More detail needed, and Andy Grove illustration Constantin Bulucea, April 25, 2016

- Possible Etchant for cleaning the surface? from Rick Dill, May 8, 2016, also Nov 21, 2016, also Dec 15, 2016

- A QUALITATIVE MODEL PROPOSAL by Constantin Bulucea - Feb-16-2017

- CP4 etchant by Rick Dill - April 17, 2017

- ... �loopy� transistor. The behavior reminds me of hysteresis in Type II superconductors. Paul Michael Grant - - Oct 6, 2017

- More e-mails - Oct 26, 2017

- e-mail thread about Russian transistors - Aug 30, 2018

- Both of the solder blobs looked very dry, dull and grainy, ... - Sept 18, 2018

- Calling the metals "solder" both totally misunderstands solder ... - Sept 21, 2018

- Meeting with Rick Dill, Constantin Bulucea, and team Mar 30, 2016

- Meeting with Rick Dill, Constantin Bulucea, and team April 6, 2016

- Commercial Experiences - May 2, 2016

- I-V Pictures and Meeting with Rick Dill, Constantin Bulucea, and team May 11, 2016

- Another model, perhaps more realistic - Constantin Bulucea, June 11, 2016

Comment on "another model" (above) - by Rick Dill - June 15, 2016

Comment on the - Comment on "another model" (above) - by Constantin Bulucea, June 20, 2016

Comment^3 model - (above) - by Rick Dill - June 20, 2016 - Documents, from Robert Garner

- Surface Properties of Germanium by Walter Brattain and John Bardeen, 1952

- Absorbsion of Water VaporOn Germanium and Germanium Dioxide JPhysChem_1959.pdf J.T. Law, 1954

- Field-Induced Conductivity Changes in Germanium Phys.Rev_1956.pdf

- Process Variables Which Affect Germanium Transistor Reliability Meet.1959.pdf

- Influence Of Hydration-Dehydration of the Germanium Oxide Layer on the Characteristics of P-N-P Transistors RCARev.1957.pdf

- Methods of Producing Stable Transistors PhilTechRev_1961.pdf

- Effect of Variations in Surface Potential on Junction Characteristics JApplPhys_1959.pdf

- Surface States on Silicon andGermanium Surfaces PhysRev_1956.pdf

- Water-Vapor-Induced n-Type Surface Conductivity on p-Type Germanium PhysRev_1955.pdf

- Some Failure Modes in Double Diffused Silicon Mesa Transistors

a 4.7 megabyte .pdf file - added July 2009

- - an abstract with images below

- Factors Affection Reliabiliity of Alloy Junction Transistors a 2.2 megabyte .pdf file - added July 2009

- Transistor Abnormalities as Revealed by Current-Voltage Characeristics a 2.2 megabyte .pdf file - added July 2009

- Some Failure Modes of Double Diffused Silicon Mesa Transistors A. A. Bergh, added Dec 2017

- - an abstract with images below

- Comments by Constantin on Shockley's 1950 "Electrons and Holes in Semiconductors"

NOT Weird Parts, but some fascinating bios

- Joseph C. Logue From Vacuum Tubes to Very Large Scale Integration: A Personal Memoir 1.7 MegaByte .pdf file

- Joseph C. Logue Oral History 4.3 MegaByte .pdf file

- as an Oral History 47 K Byte HTML file

- Constantin Bulucea (bio)

- Rick Dill (education and work bio)

- as an Oral History 47 K Byte HTML file

And - comments on a Berkeley press release

- Smallest. Transistor. Ever., Lawrence Berkeley National Laboratory, October 6, 2016

- from Constantin Bulucea

- from Rick Dill

in 2005

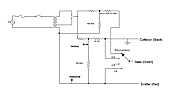

Tim Coslet is the person who fixes most of our (1401 Restoration) defective SMS cards. His primary aid is an in-circuit tester that he built from plans in the magazine ???. The write up from the trouble shooters speeds his search for bad parts. Tim, using his in-circuit tester, can get a good idea of circuit dynamic characterists with out unsoldering the parts for individual testing - a good thing! (After a part is really suspect from the in-circuit test, it is removed for individual testing and replacement.) The source of the problem is usually:

- an open diode (often cracked glass due to corrosion along the iron lead to glass interface)

- a low beta transistor unable to adequately pull down a logic line

- an open inductor

- occasionally a somewhat shorted diode that causes excessive load on the drive element

Using the in-circuit tester is not as straight forward as individual component testing - being an acquired art - but does speed diagnosis and reduces damage to parts and SMS card traces. :-))

(There have been thoughts of making SMS card testers and test programs. But with about 120 SMS card types and

several circuits per card and several tests per circuit - this would be a non-trivial task.)

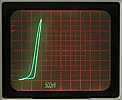

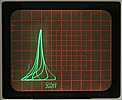

At the test frequencies and the resistances involved, the capacitors are practically open circuits and inductors are practically short circuits. These "reactive" components should not make phase changes (loops) in voltage vs. current curves at the much lower test frequency compared with the service frequencies.

And on good boards, the above expectations are met - the expected patterns on the oscilloscope are actually seen. :-))

But the world is a strange place. Many of the circuits reported bad by Ron and Bob give very unexpected patterns.

We are at a loss to explain these loops. (Thermal effects seems unlikely to provide this level of change??) Please send suggestions to Ed Thelen ed@ed-thelen.org and Tim Coslet

Added Feb 23, 2006

Further details by Tim Coslet - Feb 23, 2006

|

The original design in the magazine used +-1V peak to avoid possible damage to semiconductors during in circuit test, but this is too small to turn on darlington transistor E-B junctions so I increased my design to +-2V. I also added a +-10V peak range to check reverse breakdown, low voltage zeners, and operate transistors at higher voltages. All the 1401 testing has been done on the +-10V range, as this seemed more "realistic" to me and I was having problems getting good Beta estimates on the +-2V range (due to an effect mentioned below almost all the transistors read very low Beta on that range, but more normal Beta on the +-10V range).

The scope was not set to 1V/div. I usually use 0.5V/div when using the +-2V range and 2V/div when using the +-10V range (so the curve fits the screen better). Unless I need to determine transistor type (Si/Ge) or breakdown voltages I'm more concerned with shape than exact voltage/current levels.

E-B is the Emitter-Base junction with the Collector shorted to Base.

These are standard test definitions given in datasheets that I wired into my switch, so that I would not have to keep swapping leads around. The Beta settings use an additional similar resistor network to inject current thorough the Emitter-Base junction while the main circuit is measuring the characteristics of the Emitter to Collector path (similar to the O-B measurement, but with the Base connected instead of open). The difference in the additional similar network is that the 1K resistor is replaced by a Beta*1K resistor (50K, 100K, and 150K in my box) and there are no scope connections to that circuit. To a first approximation, if the resistor selected exactly matches the Beta of the transistor then the curve drawn will be identical to the curve drawn in E-B mode, if the resistor selected is larger than the Beta of the transistor the curve drawn falls outward, if the resistor selected is smaller than the Beta of the transistor the curve drawn pulls inward. However this is never exact as the test circuit has no compensation for the E-B diode characteristics (a second approximation effect that changes between transistor types) and the curve sometimes begins falling outward then pulls inward. A transistor on this tester should NEVER give any loops on any setting and the transistors on these cards are the first time I have encountered this! It means, for some reason, the transistor is stopping conduction far differently than it starts conduction. My suspicion is a thermal effect as I have seen many of the loops change size/shape the longer I leave the transistor on the tester. I believe you took all those photos on one transistor. -- |

March 1 update from Robert Garner

|

The 1401 transistors were germanium, although at the end of the SMS

days, silicon transistors were found that could be used as substitutes

in most cases or at least replacement boards were made with silicon

transistors that were voltage and signal level compatible.

The mode of loopy behavior in the silicon mesa transistors is similar to germanium. Mesa transistors had the collector diffused into the silicon over the entire wafer. The emitter was produced by a second diffusion or an alloy process (micro-epitaxy) and the emitter and base connections were covered with wax (or later photoresist) and were protected from an etch which went through the collector junction leaving the emitter and base on a tiny mesa of silicon. These junctions had no oxide protection except for the extremely thin native oxide and were sensitive to surface contamination as were the germanium emitter and collector junctions. The cans that transistors were put in or the plastic encapsulation of low cost transistors were to provide a hermetic seal and protect the sensitive collector junction. Contamination inside the can or any leaks resulted in leaky transistors. The experimental tools we had were primitive compared to those even a few years later when we came first to really understand silicon junction passivation by oxides and through that to have some affirmation of what was deduced from primitive experiments for unprotected silicon and germanium junctions. There were some very early lessons from the solid logic technology (SLT) planar transistors used for the IBM 360. The theory of that design was that the transistors were protected by a low temperature powdered glass layer put onto the surface and then melted to give a hermetic seal to the junctions. This in theory would stabilize the transistors, but the theory didn't work because sodium atoms in the SiO2 layer lying under the frit glass layer were mobile ... unless the transistors had that locked up in a phosphosilicate glass layer from the emitter on NPN transistors. PNP transistors didn't have problems with surface inversion and were stable without the psg layer. That really didn't come out in technical publications until the advent of field effect transistors where the role of sodium in the SiO2 layer was a major issue in controlling both leakage and threshold voltage. IBM used PSG, while Intel and others essentially eliminated sodium by lots of washing before any thermal cycle which could lock fingerprints or other sodium contamination oxides.

|

|

From the abstract, the article seems to be the first salvo in the common wisdom that "Cu is evil around Si"?:

(a) In the presence of bare copper in an oxygen free ambient, power aging degrades the emitter parameters and gain. Only partial recovery can be achieved by etching into the bulk silicon or by heating the device at 300�C (bulk failure). (b) In gold plated and/or oxygen backfilled cans, soft, loopy reverse junction characteristics develop under both temperature and power agings, first on the collector and later on the emitter. Both junctions. recover completely upon opening the can and drying the transistor surface (surface failure). Surface failure is caused by water adsorption over the surface of the silicon wafer. Experimental evidence, including aging experiments in atomic hydrogen, is presented to demonstrate that the bulk failure is caused by copper contamination in the bulk silicon. Copper is transferred from the can to the wafer via a volatile hydride. It diffuses into the silicon and becomes electrically active during power aging. Qualitative explanations are offered for both failure modes. Surface failure is due to surface states introduced by the adsorbed water and/or ionic conduction. In order to explain bulk failure, the solubility and precipitation of copper is examined over the transistor profile and the effect of field on the migration of copper in silicon is taken into account.

|

|

Lectures on Memristors, Dr. Chua added Feb 13, 2016

Here is a series of lectures

by Professor Leon Chua. And from Wikipedia.

Here is a series of lectures

by Professor Leon Chua. And from Wikipedia.

Warning: If life is comfortable and you don't want to churn up your brain, avoid this stuff ;-)) |

Dill to Garner - Re: Alloy Transistors - 09/03/2008

|

From: Rick Dill To: Robert B Garner/Almaden/IBM@IBMUS, Date: 09/03/2008 10:14 AM Subject: Alloy Transistors Robert, The early 1950's were an interesting time. In the summer of 1951, Bell Labs had a "summer school" for a fair sized group of university professors. The professor who taught optics attended and had lectures from the likes of Shockley and Bardeen as well as some laboratory hands on time. They published a paper with everyone as an author in which they confirmed the Einstein Relationship between drift of electrons and holes under electric field and thermal diffusion. They returned to campus with a small kit of experiments which a fellow student, Jim Boyden and I latched onto and used both for recreation and every opportunity for a project. We were sophomores when we got our hands on this. It included a germanium alloy diode for measuring IV curves, a chip of germanium with rhodium plating on the back (which we had to learn how to replace after etching it off) to be used for making point contact transistors, and a bar of germanium for the Shockley Hall measurement of drift and diffusion of electrons. We fabricated our own point contacts and crude manipulators to put them down near where we wanted them. In the summer of 1954. fresh with a B.S. in physics I had a job at IBM in Poughkeepsie. It was my first industrial research experience and a wonderful experience. Joe Logue was the manager of the small group which included Hannon York, the engineer who invented the current switch circuit (non-saturating), Bob Henle who was a really good circuit guy and lead the company a few years later to abandon core memories and go to semiconductor memories. At the time, the group was just off of the CRT based electrostatic memories used in the 701 and the later mica target CRT-like memories used in the following computers up to the introduction of magnetic cores which were just coming visible in 1954. My assignment was really a gift. Joe wanted higher function circuits with the example being the neon ring counter. As he has told you, with no real hands on experience I was able to postulate that we might be able to produce such a thing with a double-based diode (unijunction transistor) which had multiple emitters and with the help of the small group in the pickle factory actually get a four-state device prototyped. Dick Rutz and John Marinace were the key people in that group and I eventually ended up working for in Rutz's group. I also postulated an adder circuit based upon the Shockley Hall structure, but with deflectors to steer the electron cloud sideways to multiple collectors. We didn't make this, but it did show up a decade later as an academic achievement. While Bell Labs was stuck on point contact transistors (and even made a computer out of them), Joe Logue has recognized the superiority of junction transistors. From a circuit standpoint, the ones available had too much base resistance to work well in digital circuits, although this didn't hamper them for communications. He tried to encourage the vendors to make transistors with low base resistance to little avail since computers were not important to the electronics world at that time. The task got handed to Research where on the fabrication side the team of Rutz and Marinace and their technicians made alloy transistors with a small alloy emitter surrounded by a circular base contact, and a larger collector junction on the back side of the die. Contrary to what most people believed, alloying was a well determined metallurgical process when done right. To do it right, you needed the crystal to have a <111> orientation. This is the slow dissolving direction when subject to dissolution by molten metal, so the sides of the dissolved region were angled along <111> planes and the bottom flat. The depth depended on the volume of the alloy "dot" and the temperature. On cooling, the germanium first cleanly regrew precipitated from the melt and was doped by the materials in the dot (indium gallium for PNP transistors and tin antimony for NPN). The collector on the backside was simply larger and etched more deeply into the germanium chip. The design was IBM's, but we went to TI and contracted with them to manufacture germanium transistors for us. We were allowed only to make 10% of what we needed, which gave us room for special applications such as core drivers or advanced devices before releasing them to TI. In spite of Joe Logue trying to get me to stay and do graduate work in the Syracuse MS program, I went back to Carnegie Tech and moved from physics to EE. 18 months after that Bob Henle visited campus following up on a summer job one of the young faculty had a year after me. IBM wrote three separate contracts. One supported my research with the requirement that I come to Poughkeepsie roughly monthly to report on my progress. The other two supported Dale Critchlow, the young faculty member, and Bob Dennard, one of his students. Both Dale and Bob were working in magnetics at the time. I was the first to join IBM in February 1958 and Critchlow and Dennard joined the following summer. We were all in the same group trying to do circuits with multi-hole magnetics and transistors. I left that project in summer of 1958 to go to Poughkeepsie and work for Dick Rutz with my initial assignment being to duplicate Esaki's work in Japan on tunnel diodes. In 1955, I worked at RCA Labs for the summer on silicon diodes and the observation that they did not behave according to Shockley's theory. There I met Herb Kroemer who is credited (among other things) as the father of the "drift transistor". Kroemer postulated (as a theorist) that a graded impurity doping in the base region would provide a field that greatly speed up transistors. It was only after I got to IBM that I read a patent of Lloyd Hunter which is the patent on the structure, so IBM has at least as much claim as RCA. By diffusing (probably phosphorus) into the germanium blanks, the IBM design became much faster. In 1958 on returning to IBM, I found that the development group had built a fully automated factory for producing alloy transistors. It used syntron sonic driven bowls to feed to germanium die, alloy spheres for emitter and collector, stub leads soldered to the spheres during alloying, and the dished base contact washer. These were fed into high purity carbon fixtures, one for each transistor. Once the assembly was together it went through a hydrogen furnace, after which the transistor was extracted, etched, washed, dried, tested, and then assembled onto a header. The carbon fixture was sent back to be re-used. This room-sized automated factory could product 40 million transistors a year, which was more than IBM needed. We shipped the factory to TI with the stipulation that they could use it only for IBM production for a stated number of years. When the diffused base transistor came in, it was only a small modification to the line to get the die right-side-up so that the diffused surface was facing the emitter. About 1964 I visited TI and saw multiples of this production facility running full tilt to make germanium transistors for the world. Silicon really came in with the system 360. The group that met to work out what would be done was the Compact Committee. I was a research rep on that team. We should talk about that sometime. Bill Harding was one of the key people and I believe that he is still around in Southern CA. What became solid logic technology (SLT) came from his declaration that he could produce individual transistors very cheaply and solder them directly to substrates. This was all an act of faith, but it came to fruition and significantly delayed IBM's serious entry into integrated circuits for logic. When we did get into integrated circuits for logic, electron beam lithography played an immense role in giving IBM a competitive advantage. Hans Pfeiffer was the leader in this technology and is now in Carmel Valley. This is just a little background for out Thursday discussion. Rick |

Dill to Garner - Re: Science behind loopy transistors - 12/08/2009

|

Rick Dill 12/08/2009 09:33 PM To: Robert B Garner/Almaden/IBM@IBMUS cc Subject: Science behind loopy transistors Robert, The article by Montgomery and Brown is probably as good a reference as you will get given the understanding at the time. It is very crude experimentation with the use of a strontium titanate dielectric coupled to the semiconductor by simple mechanical contact is laughable today. Still, it does find that surface accumulation, surface depletion, and surface inversion on p-type samples which varies depending upon the ambient. It was done on high resistivity samples in order to see any significant penetration of a space charge layer into the bulk. On the other hand, the uneven gap between the dielectric and the semiconductor makes the whole thing very crude. A thin film dielectric on the surface is what is really needed to look at this phenomenon, something we didn't do until we got to silicon and then went back to with germanium. There MOS capacitance measurements can give you a good idea of the charge in the dielectric and with FETs can give you a direct measurement of the surface mobility under various conditions. Transient MOS capacitance allows you to see the recombination. But in the 1950s you didn't have those tools. I wrote a couple of the earliest papers on applications of semiconductor capacitance (voltage dependent) in 1956 and 1957. When I was playing with automated measurements in the 1970's we did automated MOS measurements including all the fun transient stuff that was new science then. We designed a mercury probe that let you make contact to a dielectric surface without having to evaporate and pattern metal. All fun and done with summer student and only ended up in internal reports. One can draw from the paper that the transistors with the biggest issues would be the npn with moisture causing a surface inversion surrounding the collector that would gobble up holes injected into the base(along with the collector, of course) and both lower the breakdown voltage at higher currents and also induce a time when they has to be drained out via a resistive path to shut off the transistor. Do we see the loopy behavior in both npn or pnp transistors. I suspect that it is most common in the former. On pnp transistors, one might expect to see the breakdown decrease with a wet ambient. There are lots of papers out there which tried various treatments and observed current gain and sometimes loopy behavior, but they weren't getting at the root cause. The big issue here is that surfaces can change charge (i.e. ionics in surface films) and this can either accumulate or invert the surface .. or sometimes the best case of leaving the bands essentially flat. Surface states and surface recombination come into play because on a surface moving toward inversion, there will be an electric field helping the minority carriers get there. This will show up as small differences in current gain. Not sure this makes sense, but the one sentence answer is: Reference 16 is about as good as you will get without some immense amount of searching. Rick It agonizes over surface states, which are probably much more important in terms of recombination and the frequency dependence than in transport of carriers. |

Dill to Garner - Re: Science behind loopy transistors - 12/09/2009

|

From: Rick Dill To: Robert B Garner/Almaden/IBM@IBMUS, Date: 12/09/2009 09:35 PM Subject: Re: Science behind loopy transistors Robert, In the late 1940's we had the Shockley "Electrons and Holes in Semiconductors" which pulled together the basic physics of motion of electrons and holes under equilibrium and non-equilibrium conditions. It only crudely handled the "forbidden" transition that caused electrons and holes to combine, behind the lifetime of minority carriers. This let us understand diodes, junction transistors, and Shockley's purely theoretical junction transistor (closest to the jfet today). It described the forward and reverse current voltage curve of germanium diodes very well with the relationship I =I0 eqv/kt Lifetime was buried in the I0 with a whole lot of hand waving and studies which identified surfaces as bad actors and talked a lot about surface states and the like. This was the physics I had when I did my PhD and the thing I never could handle was lifetime. It was a constant I could put into my equations, but I had no idea how to assign values to it. I also became aware in my 1956 summer job working for Paul Rappaport at RCA Labs that this theory didn't work for silicon diodes. The kt term became nkt where n was typically something like 2. My assignment was to make silicon diodes and measure their current voltage curves. This was one of the topics I proposed as a thesis topic, but rejected it because I didn't have a clue how to answer the question. A classic paper by Shockley, Noyce, and Sah answered that. Surface effects were largely not well understood, but the rather crude experiments in the paper you cite give a clue (largely missed). Other clues came from experiments and procedures to control base-collector breakdown. The breakdown is reduced by the geometric effects of junction curvature near the surface and also by any surface accumulation which thins the junction at the surface causing early breakdown. If the surface is depleted or inverted, the breakdown isn't affected, but the junction leakage can be high. All of this is well beyond the one dimensional theories of Shockley. Once the surface is inverted (by almost anything), then loopy behavior becomes possible. In silicon the big culprit was human sweat. Sodium on the surface (NaCl) would have the sodium incorporated in the oxide. This ion would move with field and when close to the surface would induce mirror charge in the semiconductor playing havoc with things like threshold voltage of FET transistors. Once we understood those phenomenon, the germanium story because a whole lot more understandable .. except that no one cared any more. That's it for tonight. Rick |

Meyerson to Garner - Re: Loopy I-V curves in 1950s Ge alloy-junction transistors - 04/23/2014

|

From: Bernard S Meyerson/Watson/IBM

To: Robert B Garner/Almaden/IBM@IBMUS, Gary Patton/Fishkill/IBM@IBMUS, Pmooney@SFU.CA Cc: .... Date: 04/23/2014 05:06 AM Subject: Re: Loopy I-V curves in 1950s Ge alloy-junction transistors (from our IBM 1401s at the Computer History Museum) Robert, My bet is that this originates from deep traps in the materials. At that time there was nowhere near the controls needed to prevent chemical contamination from myriad sources, and as such the traps relaxation times are what is being seen in the IV curves. What gives me reasonable confidence is that when you illuminate the transistor it suppresses the phenomena, indicating that an excess of carriers backfills states. The best way to do this is to have someone do DLTS on a dot or even a surface point contact, and Patricia Mooney might be the best person for the task. Last I heard Pat is in Simon Frasier University, I suggest you contact her and explore her having an explicit look at this. Her website is below. I also copied Gary Patton who once upon a time knew about things like transistors:-) Gary, what say you on this one? Best Regards, Bernie http://www.physics.sfu.ca/people/profiles/pmooney From the Desk of; Dr. Bernard S. Meyerson, IBM Fellow VP, Innovation IBM Corporate Headquarters 1101 Kitchawan Rd. PO Box 218 Yorktown Heights, NY 10598 Ph: (914)-945-2206 Fax:(914)-945-4245 Email: Meyerson@US.IBM.COM |

|

From: Rick Dill To: Robert B Garner/Almaden/IBM@IBMUS Cc: Constantin Bulucea Date: 03/26/2016 09:07 PM Subject: Re: Fw: Seeking semiconductor physicist to explain Loopy I-V curves in old Ge alloy-junction transistors (from our operational IBM 1401s at the Computer History Museum) I don't think that deep traps are the issue here. This was a bogeyman explanation for all sorts of problems associated with copper/gold/and-other contaminants in germanium. The ease is making germanium transistors was inadvertantly helped by the "alloy junction" process because these highly mobile materials were gettered out of the germanium into the molten metal. I (perhaps stupidly) used copper plated contacts on the unijunction transistors for my PhD work. They should have killed the lifetime in the germanium bars, needed by the device. I'm pretty sure that the copper in the germanium was gettered out. On the other hand Myerson has much more recent experience with germanium and he needs to be paid attention to. More likely, the funny loops were a function of the transistor bias cycles and surface inversion layers (which we didn't understand at all except that good clean-up etches got us good junction properties). In forward bias, these inversion layers would be well connected to the emitter and would also inject carriers into the base region (both near the narrow base junction and also outside). Turning off the emitter probably disconnected the surface inversion layer from the emitter. The excess carriers in the base (Ge has long carrier lifetime) and they would drift to the collector continuing the collector current until they were all collected or died due to lifetime. If you made transistors and etched their surfaces to a "clean" state and then encapsulated them in a can, they didn't get the moisture and "whatever" to form the inversion layers. If, on the other hand, either the solder seal of the can leaked or the iron in the leads rusted out, they would not be kept "dry". We need someone who learned from inversion layers in silicon, which became well understood some years later, to look at the funny curves and their temporal and optical behavior. I have been looking for a message verifying a time that Constantin and I might get together with you to talk about this. We started in February with a decision that Wednesdays might work. I hear nothing after my reply as to when I was available. Rick |

Dill to Garner - 03/28/2016 - More on Loopy Transistors

|

Rick Dill

Just Plain Alloy Transistors – IBM Style The 1401 came before we were doing diffusion of impurities into semiconductors. That came a little later. These were made on wafers aligned crystalographically with the surface being a <111> face. This is the slow dissolving face with many etches and also with the metals used for the emitter and collector alloy. The alloying is a crystalographic micro-etching by the metal "dots" used for emitter and collector. This gave a near-crystalographic flat bottom to the extent of the melting. The initial steps of the cooling were a recrystalization heavily doped with the appropriate impurity (gallium for pnp and probably antimony for npn). As the cooling proceeded rapidly, the melt became a mix of metal and polycrystaline germanium, getting more metallic toward the surface.

This alloying was a low temperature process done in a reducing atmosphere to help get wetting. The "clean-up" etches used afterwards were to both etch the metal back a little because it may have spread out over the base surface where there had been no alloying and also to get the surface back to an appropriate condition so that the transistor leakage at the surface was low.

The wafers were diamond cut from an oriented crystal, then mechanically polished and etched with an anisotropic etch to remove about a micron or so of lapping damage. It was fairly deep in germanium which is mechanically weaker than silicon. In the late 1960's we would have used a chemical-mechanical polish instead which was (if I remember right) a sodium hypochorite solution and a non-woven fabric pad, without any abrasive.

My frail memory cannot remember the etchants used and I haven't uncovered my PhD thesis which probably had some of the formulations in it. It hasn't been unpacked since it got moved to California a decade ago.

These wafers were then ultrasonically cut up to make round chips of controlled thickness. The polishing was probably developed by Earle Harden, a toolmaker with very skilled fingers for creating small transistors and a love for precision machining through lapping.. I first worked with him as one of my teachers and then was his manager for some years where I utilized his skills in many ways.

After he left me, he joined David Thmpson on the project that made the first thin first thin film magnetic recording heads. Earle pretty uch defined the diamond lapping process for the air bearing surface that isstill used today. I had a small role in that project. David,Luby Romankiw and I kicked over the idea of using lithography and thin films for recording heads. I had the ability to quickly make masks using the fly's eye lens which gave me a 2 micron or so capability on-axis degrading from spherical aberration. Knowing the limits and with a decision on the number of turns, I designed the masks and cut them in rubylith at 500x, so I might claim to be the designer. I made the masks after hours since it wasn't part of my day job.

The wafers were relatively lightly doped in order to get the high ration of carrier concentration between emitter and base. This was of course a compromise between current gain and base resistance. It was also the reason for the ring washer base contact. In essence, these transistors were different from any silicon bipolar transistors which always had fairly high surface concentrations surrounding the emitter which naturally came from the double diffused emitter/base and helped suppress the emission at the edges of the emitter. It also made the surface of the junction less sensitive to surface inversion.

So we have a lightly doped base region. I don't know what etchants were used, but the final etch and blow dry would be intended to leave the surface in a low leakage state at both emitter and collector. The reason for the glass metal lead header and soldered cap was to hermetically seal the transistor in an environment where it wouldn't be subject to changing moisture and other contaminants. It worked remarkably well for many years. I believe that all the "loopy" transistors we are looking at are ones which have surface contamination. While Pat Mooney is a good reference for deep level traps in semiconductors, including germanium, I don't think that is the big issue here. As I recall, Pat came to IBM and worked toward the end of the mid 1960's germanium program looking at deep traps, although we never got to long term passivation for that because silicon was close enough to Ge in speed at that time, that you wouldn't go backward for the 1.e to 2 times we eventually understood as its superiority, at least at that time. Its time may come, though. The etchant would presumable leave the surface in some sort of condition that we didn't come to properly appreciate until we made surface devices in silicon. There, with silicon oxide structures (MOS) we learned about flat band voltages and about charge creating electric fields at or above the surface. That all came in in the early 1970's.

I got to go back to my roots in semiconductor capacitance again with MOS as I had with junction capacitance. None of the MOS work was published because my real focus was on automated measurements and lithography, but it gave Thomas Garwin, a summer student, a great experience while he was deciding whether to do physics or history. He went to Harvard and did history (of science).

I believe that Hwa Yu at IBM did some work on germanium FET devices after the bipolar program. I really didn't ever talk to him much about that because his boss thought I was a traitor to kill the bipolar program I'd started when we discovered a flaw in the underlying assumptions of superiority to silicon. The problem was the limiting velocity of electrons in germanium (similar but not as abrupt as what causes Gunn Effect in GaAs).

Let me assume that the surfaces were near flat band. They would be relatively easy to move away from that if there was ionic charge at or near the surface. The light doping would make it relatively easy to either get an accumulated surface or the alternate of a depleted or inverted surface.

Since we had both npn and pnp transistors, I would expect changes due to the environment to be different for the two types of transistors, so we need to look for differences between the two and see if we can explain both phenomenon.

Let's look at the parameters. There are voltage breakdown and thermal effects on leakage. There are effects from either surface charge depletion or inversion layers. I believe that there were some papers on inversion layers and transistor turn-off, but I don't remember the terms we might have used to described them before we understood MOS.

OK .. a thought!!! You might be able to get some MOS measurements if you could take a small anodized aluminum or titanium film spot as one electrode and place it on the base surface and do a MOS capacitance measurement. It would need a soft backing to get good contact without changing the surface much. Might be too invasive. We need to think through the effect of an accumulated, depleted, or inverted surface on transistor behavior. That includes the emitter being expanded by an inversion layer which would become more conductive and inject carriers during forward bias of the EB junction. When the transistor is turned off, the inversion layer might be partly or fully cut off from the inversion leaving the inversion still emitting. This would also be a region of the transistor where the carriers take longer to get to the collector. I believe this explanation is in the literature, but don't know where to find it. It may only have been an oral paper and never published on paper.

On the other side you need to look at what a strongly inverted surface would so and whether it would affect breakdown, Particularly you might need to understand this as perhaps having a thermal sensitivity.

Finally, you need to look at the effect of saturation in the transistor. This is another circuit effect that is essentially loopy. It takes a while for the transistor to shut off. I believe that all the 1401 circuits are saturating and that there is emission into the bulk regions of the base that take time to clean out either by lifetime or carriers getting to the collector as its voltage rises.

Lots of this stuff changed a lot when we went to diffusion and epitaxial base layers with a base diffusion to lower base resistance, much less space between emitter and base contacts. And diffused emitters. At that point the impurity concentrations at the semiconductor surface were much higher.

We can learn about that era when we decide to restore one of the few Stretch or 7090 machines. Those transistors were very much like the 1401, but they had a diffused base (speeding carriers across because of its impurity gradient) and much higher impurity concentration of the base surface, even though they were structurally very similar to the 1401 transistors.

The post-alloy diffused transistors we and TI worked on in the mid 1960's were real planar structure transistors and had dimensions from lithography in the 2.5 micron range. TI was interested in low noise from low base resistance and we were interested in maximum switching speed. |