# Customer Engineering

Manual of Instruction

# Tape Adapter Unit

Tape Adapter Unit

0

0

0

TBM®

Customer Engineering Manual of Instruction

# 1.0.00 GENERAL INFORMATION . . . 1.1.00 Introduction . . . . . . . 1.2.00 Physical Description . . . 1,3,00 Machine Language . . . . 1.4.00 General Machine Logic , . . 1,4.01 Write . . . . . . . . 1.4.02 Read . . . . . . . . 1.4.03 Backspace . . . . . . . 1.4.04 Write Tape Mark . . . . . 1.4.05 Rewind . . . . . . 1.4.06 Erase . . . . . . . . . 1 1.4.07 Error Checking , . . . 1 2.0.00 TIMING AND CONTROL . . . . 1 2, 1, 00 Timing $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ 2,1,01 Read Clock . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2.2.00 Input-Output Controls . . . . 1-2, 2, 01 Interrupts . . . . . . . 1 3,0,00 FUNCTIONAL UNITS . . . . . 1 3.1.00 Final Amplifier . . . . . . . . 3, 1, 01 Amplifier Description . . . 1 3,1,02 Clipping Level Description . . . 3,2.00 Registers . . . . . . . . 1

O

٢

### MAJOR REVISION (December 1960)

This edition, Form 223-6847-2 is a major revision but does not obsolete Form 223-6847-1. Significant changes in timings have been made in this manual.

© 1959, 1960 by International Business Machines Corporation

### CONTENTS

| 5            | 3, 2, 01 | Read Registers                      | 18   |

|--------------|----------|-------------------------------------|------|

| 5            | 3, 2, 02 | Read-Write Register (R-W)           | 18   |

| 5            | 3.3.00   | Error Checking ,                    | 19 - |

| 6            | 3, 3, 01 | Vertical Redundancy Checker (VRC) . | 19   |

| 6            | 3.3.02   | Longitudinal Redundancy Check       |      |

| 6            |          | Register (LRCR)                     | 21   |

| 8            | 3.3.03   | Echo Error                          | 21   |

| 8            | 3.3.04   | Write Compate                       | 21   |

| 9            | 3.4.00   | Clocks and Counter                  | 23   |

| 9            | 3.4.01   | Read Clocks                         | 23   |

| 10           | 3.4.02   | Write Clock                         | 25   |

| 10           | 3.4.03   | Dolay Counter                       | 26   |

| 11           |          |                                     |      |

|              | 4.0.00   | INTERNAL OPERATIONS                 | 27   |

| 12           | 4.0.01   | Figure References                   | 27   |

| 12           | 4.1.00   | Basic TAU Operations                | 27   |

| 12           | 4.1.01   | Write Operation                     | 27   |

| 12           | 4,1,02   | Read Operation                      | 37   |

| $^{\perp 2}$ | 4.1.03   | Backspace                           | 51   |

| 14           | 4,1.04   | Tape Mark ,                         | 57   |

| 14           | 4.1.05   | Erase , , , , , , , , ,             | 58   |

|              | 4.1.06   | Odd Redundancy                      | 58   |

| 17           | 4.1.07   | Manual Operation                    | 59   |

| 17           | 4.1.08   | Dual Density                        | 59   |

| 17           | 4.1,09   | Rewind and Rewind Unload            | 60   |

| 18           |          |                                     |      |

| 18           | 5, 0, 00 | DIAGNOSTIC CONTROLS                 |      |

|              |          | (TAU 1 AND TAU 2)                   | 62   |

|              |          | . ,                                 |      |

### FOREWORD

This manual discusses the basic functions of the IBM Tape Adapter Unit (TAU). Because TAU can be used by several systems, no attempt is made to tie TAU to any particular system. Instead, "external system" or "external system control unit" are used to refer to an outside control.

This manual has been prepared for teaching and as an aid for learning. Engineering changes may alter timings, logic, and other information presented here; therefore, the reader should not use this information alone as a reference manual or servicing aid.

Section 1, 0, 00 of the manual covers general information and logic of TAU. Included in the general information section is an introduction to TAU and brief explanations of TAU operation.

Section 2.0,00 explains in general terms the basic timing and controls used in TAU.

Section 3.0.00 is a more detailed description of the functional units used in TAU. Included in the functional units are the final amplifier, error checking circuits and timing circuits.

Section 4.0.00 explains, in detail, TAU operations. Logic flow diagrams, block diagrams and sequence charts are included to aid the reader.

4

Section 5.0.00 describes diagnostic controls included in TAU circuits.

### 1.1.00 INTRODUCTION

The IBM Tape Adapter Unit (TAU) is a standard assembly used to control the operation of 729 II and IV tape units. TAU by itself is not a complete tape control unit, but contains all the common features found in all previous tape control units. To make TAU compatible with any particular system, the user must supply the additional control circuits specific to the operation of his system. By adding the necessary control circuits to TAU, a complete tape control unit for any system using 729 II or IV tape units can be achieved.

The common circuits contained in TAU are controls for writing, reading, backspacing, rewinding and checking. TAU has complete control of the tape unit (except for selection) and initiates all control and data flow functions from system to tape and tape to system.

Besides the basic functions mentioned above, TAU also can read and write at a high density or a low density rate on either the 729 II or IV tape units. The high density rate is 500 bits per inch and the low density is 200 bits per inch. TAU has the necessary oscillators and control circuits to switch to either density under an external command signal.

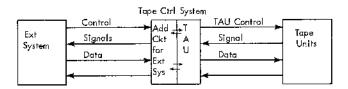

Figure 1, 1-1 illustrates the relationship of TAU to an over-all system. As can be seen, TAU has the only direct communication link with the tape unit. To perform any particular tape operation, the external system makes the request to TAU. TAU performs the operation and returns the results to the system. All data are also relayed through TAU between tape and system.

Because it is not known what systems will use TAU, timing and data lines are made available for use by the external system. These timing and data lines logically tie TAU into any added control circuits to achieve the complete tape control.

FIGURE 1.1-1. TAU SYSTEM RELATIONSHIP

### 1.2.00 PHYSICAL DESCRIPTION

TAU is an assembly of internally cabled gates. The unit is made in two forms to fit either the standard large module (sliding gate) or the standard small module (swinging gate). The card chassis assembly for the sliding gate is designed for mounting in gate positions B or D. The card chassis assembly for the swinging gate module is designed for mounting in gate positions 1, 2, 3, and 4 of the lower module.

# IBM TAPE ADAPTER UNIT 1.1.00 GENERAL INFORMATION

The names given to the two different packages are TAU 1 for the sliding gate module and TAU 2 for the swinging gate module, TAU 1 (sliding gate) contains all the basic TAU functions plus the added circuits for the dual density operation for both 729 II and 729 IV tape units. TAU 2 (swinging gate) also includes all the necessary circuits for all basic TAU functions, but because of space limitations, there are two TAU 2's. Each TAU 2 is packaged in the swinging gate module. One package is for 729 II operation at both densities and the other is for 729 IV operation at both densities. There are other minor differences between TAU 1 and TAU 2, but they are identical as to logic. Any minor variations between the two will be noted when the operations are explained in the later sections of the manual.

When the system designer mounts TAU in an available frame, he must provide the power supply, CE test panel, and external cables necessary for the efficient operation and maintenance of the unit.

The circuits used in TAU are the standard alloy junction transistor current switching circuits.

### 1.3.00 MACHINE LANGUAGE

All data registers in TAU use binary coded decimal (BCD) form. TAU operates on one character at a time. A character in TAU is made up of a 6-bit combination (B, A, 8, 4, 2, 1) and a check bit (C). The check bit can be written or read to make the bit structure either odd or even, depending upon the operation being performed. In a system not using the BCD system, the bit arrangement for the TAU registers must be performed in the external control area because information is not alter in TAU, but simply routed through in the form in which it was received.

£

്ര

### 1.4.00 GENERAL MACHINE LOGIC

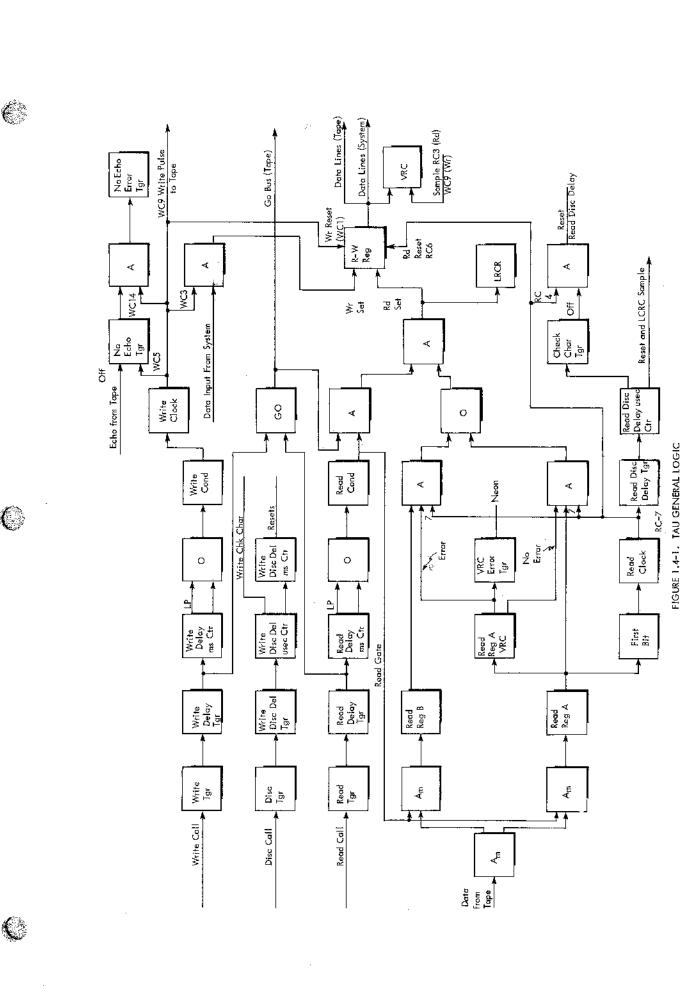

Except for selection circuits, tape units are under complete control of TAU. Any tape operation called for by an external system must make the request of TAU. Upon receiving the request for operation signal, TAU will start and control the timing and data transfer from beginning to end. TAU circuits provide all necessary timings for initiating and stopping tape movement, developing all necessary delays for any read or write operation and for all data transfer and checking procedures. Following is a logical description of TAU operations.

## 1.4.01 Write

To perform a write operation in a tape unit (Figure 1.4-1), TAU must first receive a write request signal from the system. This signal is called "write call" and initiates the proper circuits in TAU. TAU sends a "go" signal to the tape unit and tape starts moving. Because it takes time for the tape to reach its proper speed, TAU initiates a write delay before the write circuits become active. When the write delay is completed, TAU starts a write clock to control writing. Input data lines from the system are active to TAU. The write clock pulses set the data into a read-write (R-W) register in TAU. As soon as the information is in the R-W register, it becomes available to the tape unit. Another write clock pulse is developed into a write pulse and sent to the tape unit, where it initiates the writing action. The write clock, when started, is in repetitive cycles, and the writing action continues until stopped by another request signal from the system. This request signal, called "disconnect call,"

initiates circuits in TAU to complete the operation. The operation is completed by writing a check character and stopping the tape, under TAU timing control.

As data flow through TAU, error checking circuits are active to insure proper operation. These error circuits are explained in Section 3.3.00.

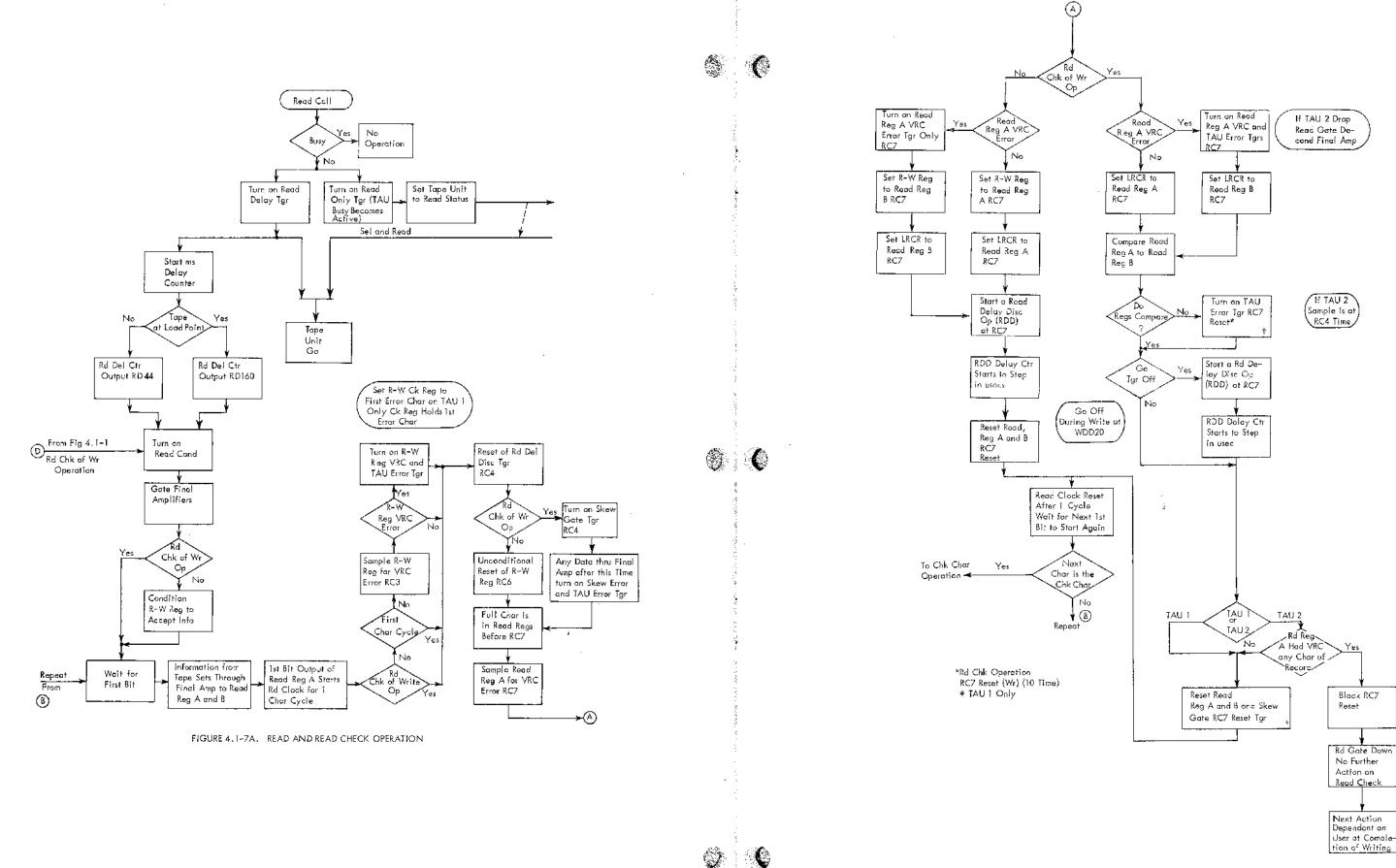

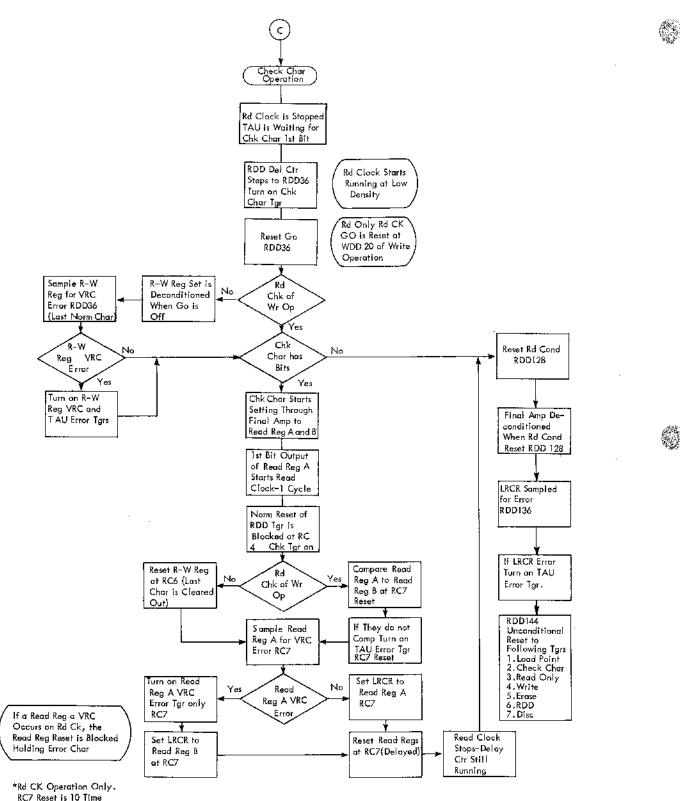

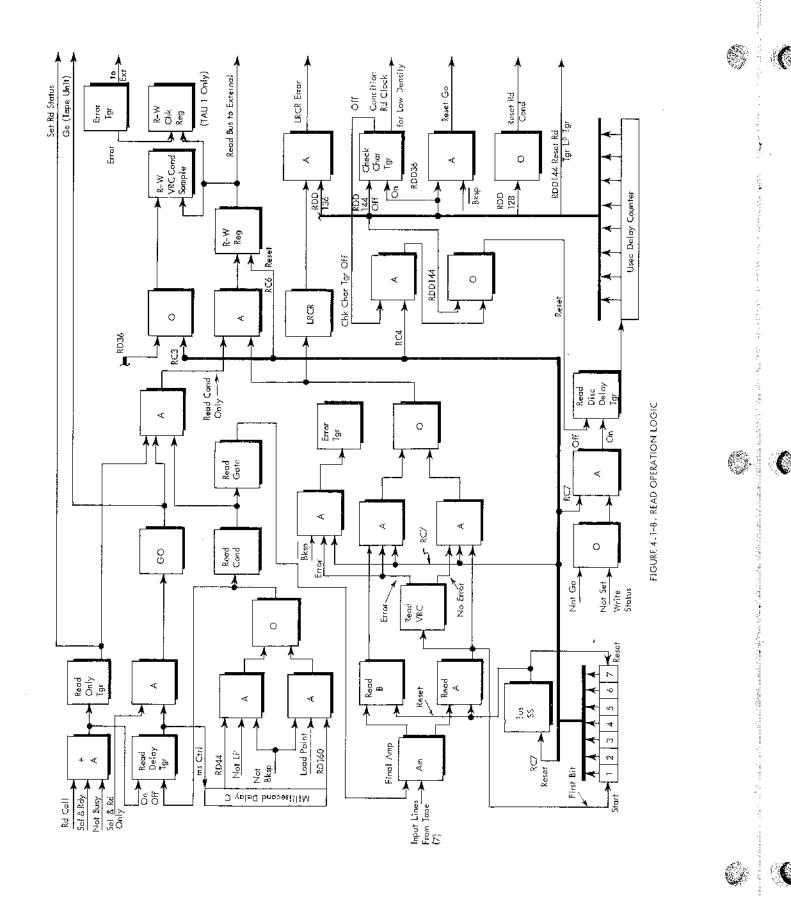

### 1.4.02 Read

A read operation (Figure 1.4-1) is started when TAU receives a "read call" signal from the system. As in the write operation, TAU develops a "go" signal to start tape moving. A read delay is initiated before the read circuits become active, to allow the tape to attain proper speed. When the read delay is completed, final amplifiers are conditioned to accept information from tape. When a character is read from the tape, it is sent to TAU through the final amplifier, and set into two registers called read register A and read register B. The two read registers have different acceptance levels to discriminate against noise pulses (read register A) and low output levels (read register B). The first character set into the read registers starts a read clock for one cycle. The read clock controls the data flow through TAU. During the read clock cycle, read register A is checked for error. If read register A is in error, a read clock pulse sets the read-write (R-W) register to read register B. If read register A has no error, the read clock pulse sets the R-W register to read register A. Once the character is set into the R-W register, it becomes available to the system. The read clock stops after the R-W register is set. The next character set into the read registers starts the clock again for one more cycle and so on, until the complete record is read. In each read clock cycle, a timing circuit is activated to try to stop the read operation, but as long as characters arrive in specified time intervals, it is reset before it can complete its function. Because the check character time is greater than the normal character time interval, the timing circuit activated during the last normal character cycle is allowed to run long enough to initiate the stopping action. The end operation circuits process the check character, perform read circuit resets, complete error checking procedures, and stop the tape.

During the read operation, error detection circuits are active to insure proper read operation. The checking procedures during a read operation are covered in Section 4.1.02.

### Read During Writing

The two-gap head on the tape unit makes it possible to read the record being written. The read portion of the write operation is used to check the record on tape for error. The write control circuits initiate a read operation. This read operation operates the same as a normal read operation, except that the data being read are never set into the R-W register. All checking of the record read is done with the data in the read registers. The write operation is not completed until the read operation is finished. The error conditions in the read check during writing are covered in Section 4.1.02.

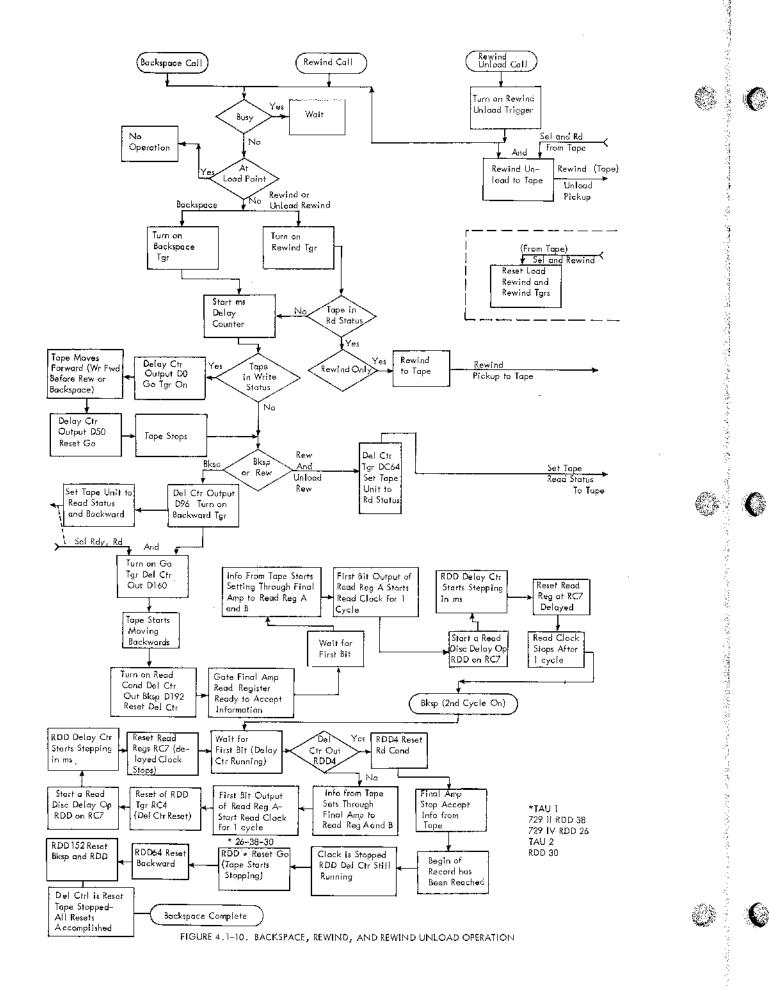

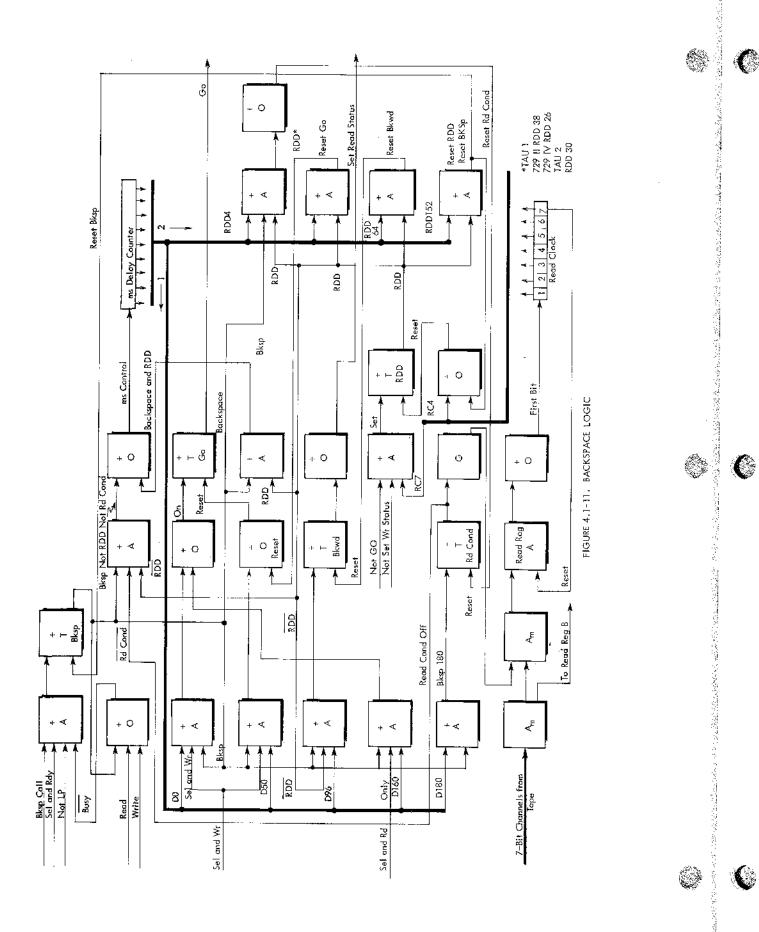

### 1.4.03 Backspace

A backspace operation is essentially a read operation in a backward direction. The only difference is that, in a backspace operation, no data are transferred from the tape to the system. The operation consists only of getting from the end of a record back to its beginning. When the "backspace call" request signal is received in TAU, the operation is started. All tape motion in a backward direction must be done with the tape unit in read status. TAU first checks the status of the tape unit. If the tape unit is in write status, TAU initiates forward tape movement for a short time before setting read status to insure that noise, created in changing to read status, will be far enough out on the tape to be erased in the next write operation. Once the tape unit is in read status, TAU will set backward status and then start the tape moving. Characters are set into the read registers and start the read clock as in any read operation. A timing circuit is started from each read clock cycle and, provided characters arrive in timed intervals, the timing circuit is reset on the next character cycle. When the beginning of the record is reached, the timing circuit stops the operation and resets the tape unit to forward status. The R-W register is not set during the backspace operation and no error checking circuits are active.

### 1.4.04 Write Tape Mark

A write tape mark operation is a one-character write operation. On receiving the write tape mark call signal, TAU activates the normal write operation circuits. Because this is a write tape mark operation, the R-W register is conditioned within TAU to set to 8, 4, 2, and 1, the bit structure of a tape mark. A write clock pulse then sets the character into the R-W register, making it available to the tape unit write circuits. Another clock output is developed into a write pulse and sent to the tape unit initiating the writing action. At the same time the write operation is started, a disconnect operation is also started to end the operation. This insures a one-character record (tape mark), and a check character is written on tape. All normal checking circuits are active.

In a read operation, TAU recognizes a tape mark and makes the recognition available to the system. In every read operation a first character trigger is turned on for the first read cycle. If the character that sets into read register A is a tape mark, a "first character tape mark" line is made available to the system.

1, 4.05 Rewind

Two rewind operations are included in TAU. One is a normal rewind operation, and the other is a rewind-unload operation. Both operations are identical for the actual rewind operation, but the rewind-unload operation causes the tape to unload.

A rewind call signal turns on a rewind trigger in TAU. The output of the rewind trigger is sent to the tape unit, where it initiates the rewind. As soon as the tape unit goes into rewind status, TAU resets the rewind trigger and the TAU operation is complete.

A rewind-unload call signal turns on a rewind unload trigger in TAU. The output of the trigger initiates the rewind action in the tape unit and, in addition, sets control circuits for unloading the tape when the rewind is completed. As soon as the tape unit is in rewind status, the rewind-unload trigger is turned off and TAU operation is complete.

### 1,4,06 Erase

An erase call signal to TAU turns on an erase trigger. With the erase trigger on, the next write operation is forced to take a longer write delay before allowing writing to begin. In effect, it causes a tape unit to skip over a section of tape.

### 1,4.07 Error Checking

In all operations where data are being transferred from TAU to either the system or tape unit, the information, while in TAU, is checked for various errors. The error checks performed in TAU consist of vertical redundancy checks, write echo checks, write compare checks, and a longitudinal redundancy check. Any of these errors turns on a TAU error trigger. The output of the trigger is available to the system, and is the only indication of an error to the external system. Besides the TAU error trigger, a read register A vertical redundancy error, a R-W register vertical redundancy error, and an echo error will turn on triggers in the TAU that are used only to light indicator lamps. Following is a description of each type of error condition.

### Vertical Redundancy Check

The vertical redundancy checker (VRC) determines the vertical bit structure of a character for either an odd or even bit count. Normally the VRC is set to check for an even bit count, but an "odd redundancy call" signal from the system turns on an odd redundancy trigger that conditions the VRC for an odd bit count. Whenever a character bit structure count does not agree with the type of vertical redundancy check called for, a VRC error line becomes active. There are two VRC's in TAU. The outputs of read register A condition one VRC and the outputs of the R-W register condition the other. Any time data appear in the R-W register they are checked. If the bit count is different from the type of check called for (odd or even), a clock pulse samples the error line and turns on the TAU error trigger and the R-W register VRC error trigger. The R-W register VRC error trigger is used only as a neon indication on the TAU wiring panel.

In any read operation, the output of read register A is checked. If a vertical redundancy error exists in a read check during writing operation, the TAU error trigger and read register A VRC error trigger are turned on. If the error exists in a normal read, the read register A VRC error trigger is turned on but the TAU error trigger is not. The VRC error line in a normal read is used to gate the outputs of either read register A (no error) or read register B (error) to the R-W register.

### Echo Check

To insure that something is being written on tape during a write operation, TAU checks for return echoes from the tape unit. During the write operation, a no-echo trigger is turned on. When writing takes place in the tape unit, the tape write circuits develop an echo and return it to TAU. Any echo return will reset the no-echo trigger. If the tape writing circuits are not active, no echoes are developed and the no-echo trigger remains on. At the end of the write cycle, the no-echo trigger output is sampled. If the trigger is on, the echo error and the TAU error triggers are turned on.

# Write Compare

While read checking during a write operation, the character in read register A is compared against the character in read register B. If they are not alike, the TAU error trigger is turned on.

### Skew Error

A skew error trigger is turned on whenever bits appear after a normal character gate time. The read clock allows a definite amount of time to read all bits of any one character. After this time, all bits of any character should have been read. If any bits appear after this time, the skew error and TAU error triggers will be turned on.

Longitudinal Redundancy Check Register (LRCR)

The LRCR is a seven-trigger binary register which keeps an odd-even count of each bit track. The count of bits in a horizontal track in a write operation should always be even. Assuming no error, the record that is read should also have an even count for each bit track. Before completing any read operation, the LRCR output is sampled. If any trigger is on at this time, the TAU error trigger will be turned on.

1.4.08 Dual Density

The dual density feature of TAU allows TAU to write and read either the 729 H or IV tape units at a high density rate (556 bits/inch) or a low density rate (200 bits/inch).

TAU 1 contains all the necessary circuits to operate both 729 II and IV tape units at either density. Because of space limitations, TAU 2 is packaged to operate on 729 II at either density and another TAU 2 is necessary to operate 729 IV tape units at either density.

### TAU 1

A request signal from an external system is received by TAU and sent to the tape unit hi-lo density trigger. The status of the density trigger, returned to TAU, together with the select and ready line of either the 729 II or IV tape unit, conditions the proper oscillators in TAU. The conditioned oscillators feed the read and write clocks and other timing circuits necessary to time TAU to the correct density.

### TAU 2

The dual density operation for TAU 2 is identical to that of TAU 1 except that the "sel and ready mod" tape unit is not used to condition the oscillators. This line is not necessary because there is a separate TAU 2 for each tape unit. On TAU 2 the density line from the tape unit serves only to condition the proper oscillator for either density whereas in TAU 1 the proper oscillator for 729 II or IV operation, as well as the dual density condition, had to be met.

### 2.0.00 TIMING AND CONTROL

### 2.1.00 TIMING

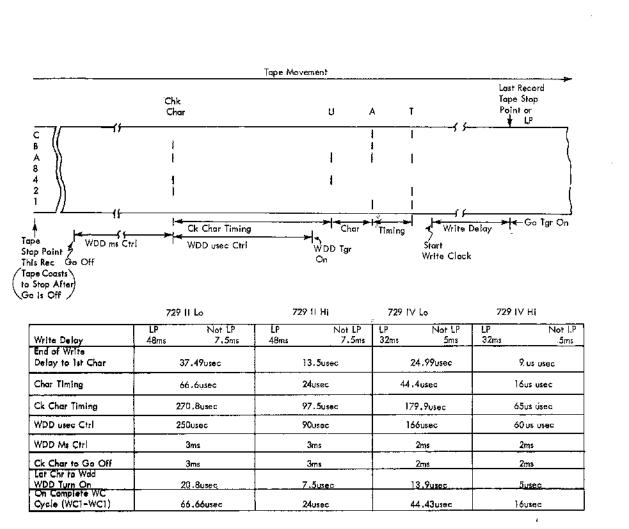

All the necessary timings and delays required by TAU are generated by oscillator driven binary counters. The timing circuits included in TAU consist of a read clock, a write clock and a delay counter. Because TAU can operate with 729 II and IV tape units at either density, the timings of the various control circuits must vary. By selecting different oscillators, the output of the timing circuits can be varied. Figure 2.1-1 lists the timings and clock pulses for the two different tape speeds at both densities.

### 2.1.01 Read Clock

The read clock is a four-stage modified binary counter. The clock triggers are labeled RC1, RC2, RC4 and RC8. By gating combinations of the four triggers, pulses from RC1 through RC11 can be obtained. All timings from the read clock will be referred to as RC1, RC2, RC3, and so on to RC11.

Each first bit of a character read during a read operation allows oscillator drive pulses to start stepping the clock. All necessary timings required for data flow and checking on any read operation are obtained from the read clock.

### 2.1.02 Write Clock

The write clock is a four-stage modified binary counter. Write clock triggers are labeled WC1, WC2, WC4, and WC8. As in the read clock, by gating combinations of the triggers, pulses from WC1 through WC15 can be obtained. All write clock pulses will be referred to as WC1, WC2, WC3, and so on.

Early in a write operation, TAU turns on a control trigger (write condition) which gates oscillator drive pulses to the clock. Since the clock is a binary counter, 16 drive pulses are necessary for one complete cycle. As long as write condition remains on, the clock is in repetitive cycles. When the write operation is ending, write condition is turned off and the clock stops. The clock input is gated also with the WC8 trigger, which insures that all clock triggers are off when the clock stops. All timing pulses for data flow through TAU during a write operation are obtained from the write clock.

### 2,1,03 Delay Counter

The delay counter is a 9-stage modified binary counter. The delay counter triggers are labeled in binary order from DC1 to DC256. Since the delays required by TAU range from microseconds to milliseconds, the delay counter can count in both the microsecond mode and the millisecond mode. It also has facilities for starting and stopping at any specified point in a cycle. The outputs of the delay counter are obtained by gating combinations of the triggers. Because the delay counter is widely used in all TAU applications, the outputs are labeled according to the gating lines and the count at

| DELAY | C |

|-------|---|

|        | 729 II Lo | 729 II Hi | 729 IV Lo | 7 <b>2</b> 9 [∨ <b>H</b> [ |

|--------|-----------|-----------|-----------|----------------------------|

| Osc    | 240KC     | 667KC     | 360KC     | 1MC                        |

| RDD36  | 150usec   | 54 Qusec  | 100usec   | 36.0usec                   |

| RDD128 | 532use⊂   | 192 usec  | 355usec   | 128.0usec                  |

| RDD136 | 566usec   | 204usec   | 377usec   | 136.0usec                  |

| RDD144 | 60Cuse c  | 216usec   | 400usec   | 144.0usec                  |

| WDD60  | 250usec   | 90µsec    | lóóusec   | 60.0usec                   |

|               | 729 []        | 729 IV        |

|---------------|---------------|---------------|

| Osc           | 667KC         | 10KC          |

| RDD4          | .6ms          | 0.4ms         |

| RDD26 + RDD38 | 5.7ms (RDD38) | 2.6ms (RDD26) |

| RDD30*        | 4.5ms         | 3 . Oms       |

| RDD64         | 9.6ms         | 6.4ms         |

| RDD152        | 22.5ms        | 15.2ms        |

| WDD20         | 3.0ms         | 2 .Oms        |

| RD44          | 6.6ms         | 4.4ms         |

| RD160         | 24 . Oms      | 16.0ms        |

| WD52          | 7.8ms         | 5.2ms         |

| WD80          | 12nis         | 8.0ms         |

| WD320         | · 48ms        | 32ms          |

| D50           | 7.5ms         | 5.0ms         |

| D96           | 14.4ms        | 9.6ms         |

| D160          | 24 . Oms      | 16.0ms        |

| Bksp 180      | 27 . Oms      | 18.0ms        |

| 5t Rd Cond 32 | 4.8ms         | 3.2ms         |

\* TAU 2 only

| Timing Ref<br>Rise of 1st Bit | 729    La | 729 II Hi | 7 <b>29</b> [V Lo | 729 IV Hi |

|-------------------------------|-----------|-----------|-------------------|-----------|

| Ose                           | 240KC     | 667KC     | а з <b>6</b> 0КС  | lmeg      |

| RC3                           | 12.8usec  | 4.8usec   | 8.6usec           | 3.3usec   |

| RC4                           | 16.9usec  | 6.3usec   | 11.4usec          | 4.3usec   |

| RC5                           | 21.lusec  | 7.8usec   | 14.lusec          | 5.3usec   |

| RCó                           | 25. Jusec | 9.3usec   | 17.Ousec          | 6.3usec   |

| RC7                           | 29.5usec  | 10.Susec  | 19.7usec          | 7.3usec   |

| RC7                           |           |           |                   |           |

| Reset (Rd)                    | 31.6usec  | 11, ousec | 21. Jusec         | 7.8usec   |

| RC7                           |           |           |                   |           |

| Reset (Wr)                    | 44usec    | 16. Tusad | 29.Susec          | 10.8usec  |

| Timing Ref      |           |           |           |           |

|-----------------|-----------|-----------|-----------|-----------|

| Rise of Ist Bit | 729    Eo | 729    Hi | 729 IV Lo | 729 IV Hì |

| _               |           |           |           | _         |

| Osc             | 240KC     | 667KC     | 360KC     | Imeg      |

| WC1             | Reference | Reference | Reference | Reference |

| WC3             | 8.32usec  | 3.00usec  | 5.56usec  | 2.00usec  |

| WC5             | 16.6usec  | 6.00usec  | ]].lusec  | 4.00usec  |

| WC9             | 31.5usec  | 11.5usec  | 21. Jusec | 7.75usec  |

| WC14            | 54. lused | 19.5usec  | 36.lused  | 13.0usec  |

| WC15            | 66.6usec  | 24.0usec  | 44,5usec  | 16.0usec  |

FIGURE 2.1-1. TIMING RELATIONSHIPS

### COUNTER USEC CTRL

### DELAY CTR MILLISEC CTRL

### READ CLOCK OUTPUT

### WRITE CLOCK OUTPUT

the output circuit. Listed in Figure 2.1-1 are the timing outputs for 729 II and IV operation.

The counter operation is controlled from control triggers turned on during specific TAU operations. Depending upon the timing necessary, either millisecond or microsecond control is conditioned by the controlling trigger. The millisecond or microsecond control gates the proper oscillator drive pulses to the counter. The drive pulses are obtained from outputs of six oscillators. Three oscillators are used for 729 IV operation for the millisecond and microsecond mode, and three oscillators are used for 729 II operation in the millisecond and microsecond mode. The correct oscillators are conditioned by a "sel and rdy Mod II" from the tape unit. All outputs of the delay counter are used to obtain all the delays for tape motion and for completing TAU operations.

### 2.2.00 INPUT-OUTPUT CONTROLS

Input data and control lines to TAU from the external system are listed in Figure 2.2-1. Also listed are all output lines from TAU to the tape unit. The timing and control data lines required by the external system from TAU are made available at edge connectors. Figure 2.2-2 lists all the lines that are available at the edge connectors.

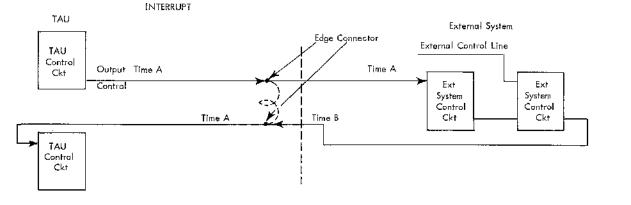

### 2.2.01 Interrupts

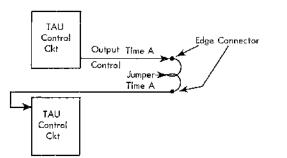

The pulses and control lines listed in Figure 2.2-3 are interrupt lines made available by TAU. These lines are normally jumpered closed at edge connectors with no change in function. However, when an external system wishes, the interrupt line may be broken and used for a control purpose in the external system. The result of the logic circuit in the external system must be tied back to TAU and complete the function which the interrupt line normally completed, as illustrated in Figure 2.2-4. The basic logic of TAU that is controlled by interrupt lines can be altered by an external system. Because it is impossible to cover all cases when the interrupts are used, the line names in TAU are always labeled as if the line were not interrupted. It is recommended that in study of TAU, in any particular system, the reader familiarize himself with the interrupt lines and their related function and timing in TAU. All illustrations in the manual are treated with the understanding that none of the interrupt lines have been interrupted.

# 0 (

| FROM CONTR           | FROM TAPE UNIT    |                  |

|----------------------|-------------------|------------------|

| Early Sample         | Machine or Pwr-On | Data Lines       |

| Amplifier Bios       | Reset             | Write Echoes     |

| Data Lines           | Reg A Only        | Sol and Rdy M4   |

| All Request Signals  | Reig B Only       | Sel and Rdy M2   |

| Turn on TI           | Compare C.K.      | Sel and LP       |

| Turn Off TI          | Sel and Rdy MIV   | Sel, Rdy and Rd  |

| Manual Op            | Sel Rdy and Rd    | Sel, Rdy, and Wr |

| Manual Data Lines    | Sel Rdy and Wr    | Sel Not LP       |

| Manual Write Disc    | Set Hi Density    | Sel and TL Off   |

| Manual Stop of Error | Set Lo Density    | Sel and TLOn     |

| Manaul Error Reset   | Thermal Interlock | Hí Density       |

|                      |                   | Set and Rewind   |

FIGURE 2.2-1. TAU EXTERNAL INPUTS

| TO CONTROL UNIT |               |                   |  |

|-----------------|---------------|-------------------|--|

| RC3             | WD            | Go Reset          |  |

| 806             | WD52          | Set Read Status   |  |

| WC5             | WD80          | Read Condition    |  |

| WCI             | WD768         | Set Write Status  |  |

| WC9             | WDD           | Erase             |  |

| Write Pulse     | WDD20         | Backspace         |  |

| WC14            | WDD60         | Backward          |  |

| DC8             | Data Lines    | Rewind            |  |

| DC16            | Check Char    | Rewind Read       |  |

| DC32            | First Char TM | Rewind-Unload     |  |

| DC64            | Error         | Sel and Rew       |  |

| DC128           | Busy          | Sel and Not LP    |  |

| RDD             | Load Point    | Sel and Ti On     |  |

| RDD36           | Sel and Load  | Sel and TI Off    |  |

| RDDI28          | Point         | TR Reset          |  |

| RDD136          | Write Igr     | Echo Error        |  |

| RDD144 Only     | Go            | Thermal Interlock |  |

| us Sample       |               | Reset WR Tgrs     |  |

| RDD152          |               | High Density      |  |

|                 | TO TAPE UNIT  |                   |  |

| Write Bus       | Reset Wr Tgrs | Rewind-Unload     |  |

| Ga              | Write Pulse   | Turn Off TI       |  |

| Set Rd Status   | Backward      | Turn On TI        |  |

| Set Wr Status   | Rewind        | Set Hi Density    |  |

|                 |               | Set Lo Density    |  |

FIGURE 2.2-2. TAU EXTERNAL OUTPUTS

|                   | Eunction                             |  |  |  |

|-------------------|--------------------------------------|--|--|--|

| Name              | Function                             |  |  |  |

| RC7               | Turn on Read Disc Dly                |  |  |  |

| Write Condition   | Develop Wr Clock Sample              |  |  |  |

|                   | Write Clock Drive                    |  |  |  |

| WC3               | Set R/W Register to Input Data       |  |  |  |

| RDD TR Reset      | Reset Rd Disc Delay (RDD)            |  |  |  |

| RDD144 Delay      | Reset Rd Disc Delay (RDD)            |  |  |  |

| RDD4              | Reset Read Condition                 |  |  |  |

| Ungaged VRC       | R/W Register VRC Error               |  |  |  |

| Read LRCR Error   | Error Line                           |  |  |  |

| Error             | Turn on TAU Error Tgr                |  |  |  |

| Bksp or Rewind    | Busy                                 |  |  |  |

| Sel and Ready     | Read Only Trigger                    |  |  |  |

|                   | Initiate Read Delay<br>Write Trigger |  |  |  |

|                   | Initiate Write Delay                 |  |  |  |

|                   | Write TM                             |  |  |  |

|                   | Erase                                |  |  |  |

|                   | Backspace                            |  |  |  |

|                   | Jurn On Rewind Trigger               |  |  |  |

|                   | Jurn On Rewind Unload Tar            |  |  |  |

|                   | Juli on Kennia onioae Igi            |  |  |  |

| TAU 2 INTE        | RRUPTS                               |  |  |  |

| Name              | Function                             |  |  |  |

| Oscillator        | Read Clock Drive and Sample          |  |  |  |

| Write Condition   | Wr Clock Drive and Sample            |  |  |  |

| WC1               | Reset R/W Register                   |  |  |  |

| Micro-Sec Pulse   | Delay Counter Drive Pulse            |  |  |  |

|                   | Write Clock Pulse                    |  |  |  |

| Milli-Sec Pulse   | Delay Counter Drive Pulse            |  |  |  |

| TR Reset          | Resot Odd Redundancy Tgr             |  |  |  |

| R/W Reg Error VRC | R/W Reg Error Tgr                    |  |  |  |

| }                 | TAU Error Tgr                        |  |  |  |

| Read LRCR Error   | TAU Error Tgr                        |  |  |  |

FIGURE 2.2-3. TAU INTERRUPTS

÷

÷.

# 3.0.00 FUNCTIONAL UNITS

# 3,1.00 FINAL AMPLIFIER

Each of the seven final amplifiers is fed from the 7-bit read bus channel from the tape unit. The inputs to the amplifiers are peak amplitude sensed. The final amplifiers have two outputs, a high level and a low level. Seven high and seven low output signals are developed for input to the read registers.

3.1.01 Amplifier Description

The basic TAU final amplifier consists of three SMS cards. Each card serves a specific function in the operation between the input read bus and the output pulse used to set the read registers.

Two more cards are added to each of the basic amplifiers to make the second channel of the dual channel system.

The first card (AFC) is used to perform the five functions listed below.

- 1. Amplify the input signal 2, 2 to 2, 4 times (transformer).

- 2. Provide two signals 180<sup>°</sup> out of phase (transformer).

- control cards).

- emitter followers).

- (high and low clipping channels).

The normal read signal input is eight volts peak-to-peak and all acceptance level percentages are based on this figure. The sine wave frequency range for proper operation is 7.5kc to 32kc. This range of frequencies is designed to provide maximum reliability for operating 729 II and 729 IV Tape Units.

The noise clipping applied to the first card is provided by three external cards which can be varied over a wide range of values. The clipping value is switched between read and write operations to the values shown below.

| Clippin | g Level j | ( <b>-</b> 12v Ref | erer | ice) |

|---------|-----------|--------------------|------|------|

| Write   |           | Read               |      |      |

| -2.4v   | в         | 6v                 | в    |      |

| +1.2v   | A         | +2.2v              | А    | Ad   |

| +2.4v   |           | +0.6v              |      | + ;  |

| +3,6v   | А         | +2.8v              | Ā    | Εf   |

|         |           |                    |      |      |

The output of the first card is the half wave of the input amplified twice.

The second card (FC) provides two functions for the final amplifier system: Differentiation and clamping Amplification and integration

FIGURE 2.2-4. INTERRUPT LOGIC

3. Impress a DC bias to provide a noise clipping level (transformer plus external

4. Rectify out-of-phase signals to provide in-phase signals (first transistor stage-

5. Provide two outputs, one of which is impressed with additional noise clipping

dditional clipping provided to channel A inverse channel B clipping voltage ffective clipping for channel A

The time constant of the differentiation is selected to provide a flat response over the frequency range mentioned. After differentiation, the negative portion of the signal is clamped out. The positive portion is amplified about 20 times and integrated in the emitter follower output stage. This provides a signal output that has a fall time coineident with the input peak and, as such, is an effective peak senser. The integration provides a sharp cut-off to frequencies above the band pass to protect the system from noise.

The third card (FD) provides two functions:

DC sensing Pulse generation

The input circuit to this card is essentially a Schmidt trigger. The input signal will charge the integrator of the previous card from -12 volts towards -6 volts. When the signal rises to about -10 volts, the trigger will turn on. Because the rise of the integrator is slow and the fall fast, the time difference between the input peak and the fall of the trigger is more consistent. It is for this reason that the fall of the input signal is used to form the output pulse. The pulse is generated in an LC timing network and has a duration of about 0.6 usec.

3.1.02 Clipping Level Description

Four cards are used to establish the various clipping levels used in TAU.

The basic card (WU--) affects the clipping level of both the A and B channels. This circuit contains a voltage divider and a transistor switch which can be activated, when required, to alter the divider output. As presently used, the switch is turned on when TAU is in 'not write status." This results in less clipping voltage at the output.

A second card (ABP-) is connected in parallel with the basic card to further control the clipping voltage. The card has a number of output voltage possibilities and can be switched independently of the basic clipping card.

Because the two cards previously explained affect both channels equally, a second set of cards is necessary to control the relationship between the A and B channels.

These cards (ABQ- and ABR-) impress a positive bias on the output of the AFCamplifier card in order to produce additional clipping on the A channel when the B channel is operating at a very high sensitivity. As in the case of the previous cards, these cards are switched when not in write status.

### 3.2.00 REGISTERS

### 3, 2, 01 Read Registers

TAU has two read registers; one, read register A, is set from the high level output signals from the final amplifier, and the other, read register B, is set from the low level output signals from the final amplifier. Each read register contains seven triggers, one for each bit of the 7-bit code. Because of skew on the tape, the character bits remain in the read registers for a length of time determined by the read clock cycle. This is done to insure that all the bits of a particular character have been re-

### 18

ceived by TAU, before the character is placed in the R-W register. The length of time the character bits are allowed to remain in the read registers is a little less than half of the normal character time interval. If the full character is not in the read registers by this time, an error is indicated in the read cycle.

In a normal read, the character in either read register A or read register B is gated to the R-W register. If the character in read register A is correct (no vertical redundancy error) it is sent to the R-W register; however, if the character in read register A is not correct (read register A vertical redundancy error), the character in read register B is unconditionally sent to the R-W register. When the R-W register is set, the LRCR is also set. The operation is the same for a read check during writing operation, except that the character is sent only to the LRCR and not to the R-W register.

3.2.02 Read-Write Register (R-W)

The R-W register is a group of seven triggers, one for each bit of the 7-bit code. All data passing between the external system and a tape unit pass through the R-W register. The R-W register is the swinging door through which the data are allowed to flow either way. During writing, the input data lines are set into the R-W register, and the register output is the data output of TAU to the tape unit. During reading, the R-W register is set from the read register and the R-W register output is again the output of TAU, only this time to the external system.

3.3.00 ERROR CHECKING

3.3.01 Vertical Redundancy Checker (VRC)

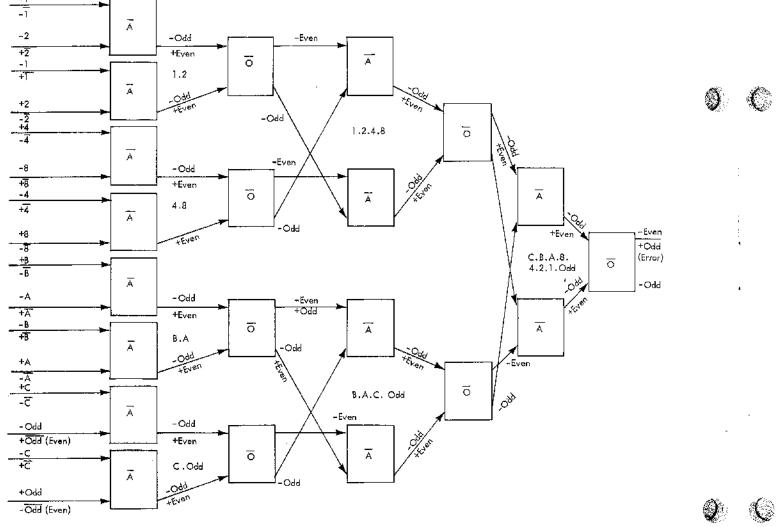

The outputs of read register A and the R-W register feed VRC's. Both VRC's are conditioned by an odd redundancy trigger that can be turned on and off by the external system. The VRC's are a combination of plus and minus OR circuits that determine the vertical bit structure of a charactor. The output of the VRC is an error line. By use of the odd redundancy trigger, the VRC error line can be conditioned to be active for either odd or even redundancies.

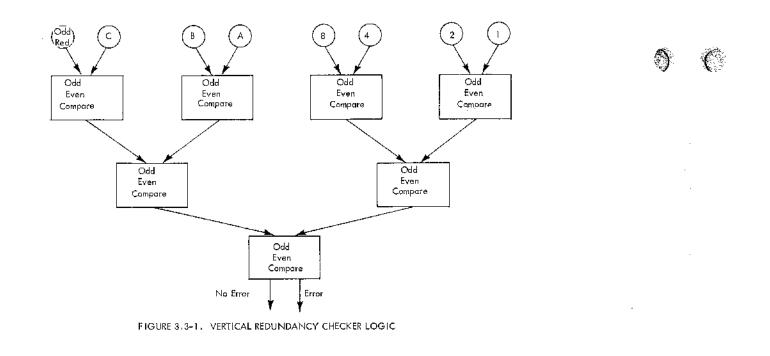

Figure 3.3-1 shows the VRC circuit used in TAU. The inputs to the checker are the seven bit lines of the 7-bit code and the odd redundancy conditioning line. The bits are compared in pairs for even or odd outputs. The results of two group comparisons are then compared in pairs for even or odd outputs, to give two final groups which are also compared for the odd-even result. The final result of the last comparison is the output of the VRC.

Figure 3.3-2 shows the second-level logic of the TAU VRC. The labels above the input lines show the condition of the lines when the input is active. The names below the line represent the condition of the line when the input is inactive. The outputs of the AND blocks are considered odd if only one of the inputs is present, and even if none or both of the inputs are present. The status (plus or minus) is the level of the line when the given condition is present. The odd redundancy input is used to condition the C bit input to check for either the odd or even redundancy check.

FIGURE 3.3-2. VERTICAL REDUNDANCY CHECKER (VRC)

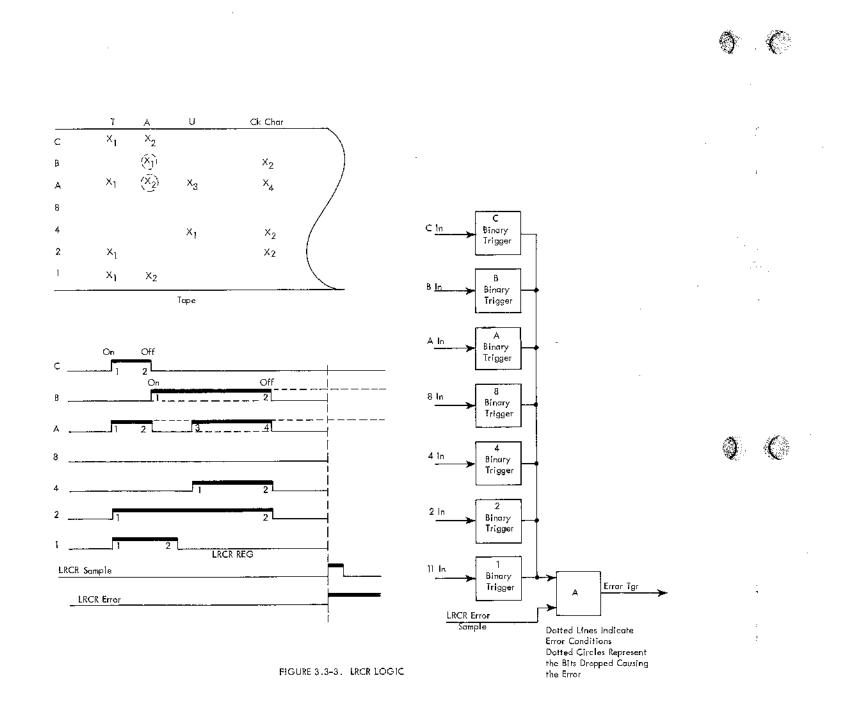

3.3.02 Longitudinal Redundancy Check Register (LRCR)

The LRCR is a group of seven triggers, one for each bit of the 7-bit code. All the triggers are binary triggers. At the start of any read operation all triggers are off. As character bits are set into the LRCR, each trigger being set will be turned on with the first bit, off with the second, on again with the third, and so on throughout the record. Since a record, when written, is always made even when the check character is written, the LRCR, after setting to the check character, should finish with all triggers off (even count). If this is the case, no error is indicated. However, if any trigger is on after the check character sets, the active trigger output will indicate an LRCR error.

Figure 3.3-3 illustrates the LRCR action with a simple record, on tape, as shown at the upper left. When the record is read, each character is checked for a VRC error as well as the LRCR error. All bits have an even count both vertically and horizontally. The action is noted in the sequence chart below the tape. In the A track, as an example, the first A bit read will turn on the A trigger in the LRCR. The second bit read will turn the trigger off, the third A bit will turn the trigger on, and so on through the record. At the end of the record the trigger in the LRCR will contain an odd or even count of each bit track just read. When the check character is read, any triggers which were on will be turned off.

The dotted circles note the bits which are dropped to indicate an LRCR error. Two bits are shown being dropped to indicate that the character is still even vertically and a VRC will not occur. The dotted lines represent the error condition in the sequence chart. Notice that when the LRCR sample is active the B and A triggers are on and an error will occur. If only one bit had failed to read, the record would indicate a VRC as well as the LRCR. With only one bit dropped, the second character would have an odd bit count causing the VRC error. The LRCR would still show an error because the bit track in which the bit was dropped would have an odd horizontal count.

The logic diagram at the right of Figure 3.3-3 shows the LRCR register and the sample. If any trigger has an output when the register is sampled, the A circuit will have an output to turn an error trigger on. The LRCR is always sampled well after the check character is read, to insure that all characters have been entered.

3.3.03 Echo Error

In each write cycle, a no-echo trigger is turned on before sending a write pulse to the tape unit. When any writing takes place on the tape unit (from a TAU generated write pulse), the active write circuits develop an echo pulse and send them to TAU. Any echo pulse received by TAU resets the no-echo trigger. Late in the write cycle the status of the no-echo trigger is sampled. If the no-echo trigger is on, the TAU error trigger and a no-echo error trigger will be turned on. If the trigger is off (echo return), no error will be indicated.

### 3.3.04 Write Compare

In every read during a write operation, read register A and read register B are compared with each other. Any uneven comparison will indicate an error by turning on the TAU error trigger. The compare circuit is a group of -AND circuits conditioned by the outputs of both registers. By allowing the read circuits to become active earlier than normal, a compare check is used to detect inter-record gap noise.

### 3.3.05 Skew Error

As a check against any excessive speed variation of tape movement between the write and read heads, a skew error circuit is used. A momentary slow-down of the moving tape at the time of writing will cause the written characters to be spaced closer together. If the tape is traveling at normal speed when the characters are read, a skew error will result. The momentary slowing down of the moving tape arises if the tape driving mechanism should momentarily slip or bind. During this period when tape is traveling at a slower rate, less tape is passing under the write head. With the write pulse frequency remaining constant, the magnetized areas on the tape speed and writing frequency. When the tape unit is back at its normal speed, the closer spaced characters will have a smaller time interval between them. The reading circuits were designed to accept characters at the normal time interval. If any characters appear earlier than the normal time interval, the skew error circuit will become active.

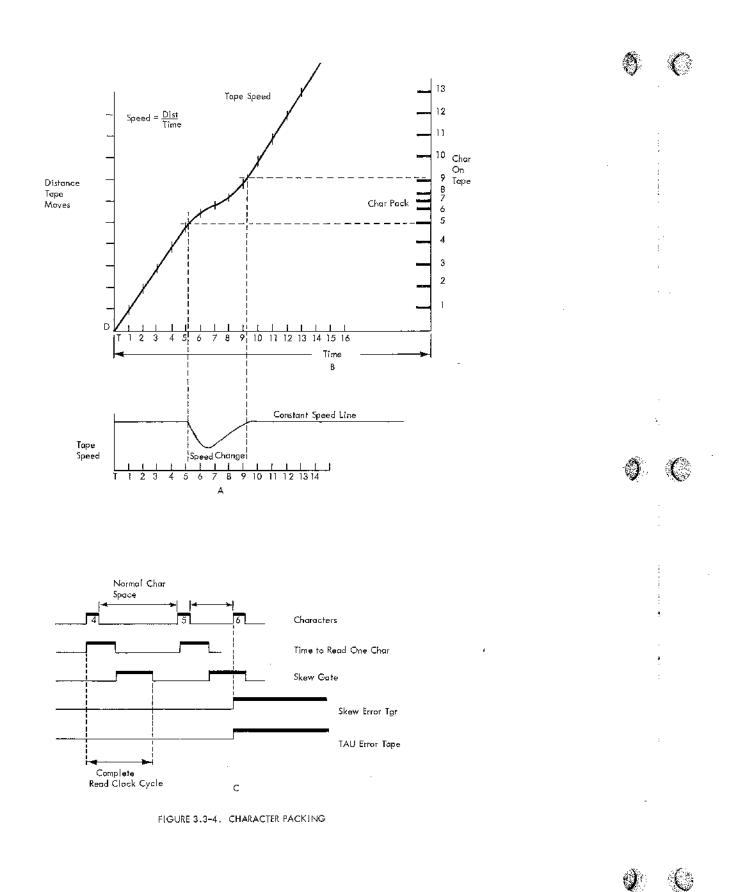

Figure 3.3-4 illustrates the action. In graph A is a typical tape envelope (ignoring start time). The tape speed is constant until T5 time, where the slowing down takes place. At T9 time the tape is traveling at its normal speed.

Graph B is the speed line. Speed is a function of distance traveled, divided by the time. Any point on the graph up to T5 shows the distance tape travels with respect to time and is directly proportional. The ratio is a constant denoting that the tape is travelling at a constant speed. From T5 to T9, however, is the slowing down point. The graph illustrates that, for a given time, the distance travelled is much less at the T5 to T9 time. If characters are written at timed intervals and plotted on the graph, the character spacing would be as illustrated on the right end of the graph.

Chart C shows the error circuit action when these characters are read. Only characters 4, 5, and 6 are shown in the sequence chart. When the first character is sensed, a read clock cycle is started. A portion of the read clock cycle is allotted to allow time for all bits of a character to be read. At the completion of this time the character is placed in the R-W register. Also, at this time, a skew gate trigger is turned on to check for the error condition. Since characters 4 and 5 are spaced correctly apart, a skew error is not indicated. However, characters 5 and 6 are spaced closer than normal. Character 6 will be read when the skew gate is active and turn on the skew error and TAU error triggers. Character 6 was written when the tape had slowed down and the condition has been noted by the skew error condition. Characters 6, 7, and 8 are shown packed together. This is referred to as bit or character packing.

This circuit is active only when a momentary slow-down of tape occurs. There must be an excessive speed change in tape movement between the write head and the read head,

3.4.00 CLOCKS AND COUNTER

3.4.01 Read Clock

**X**,

The read clock in TAU consists of four binary triggers separated by a 400 nanosecond delay line. The high-low density line and the selected tape unit (II or IV) determines one of four oscillators used to obtain the drive pulses. The oscillator output is fed to a 400 nanosecond\* single shot where the drive pulses are developed. The

\* One nanosecond equals one milli micro-second.

400 nanosecond drive pulses feed all four triggers in parallel. Because of the 400 nanosecond delay between each clock trigger, the only trigger conditioned when the drive pulse arrives will be the only one set. The previous trigger will be reset by the same pulse. When any one trigger is set, the next trigger in the ring is conditioned after the 400 nanosecond delay. By this time, the drive pulse has disappeared and another drive pulse is necessary to set the next trigger. By this method, then, the first drive pulse will turn on the RC1 trigger, the second drive pulse will reset RC1 and turn on RC2, the third will turn RC1 back on (RC1 and RC2 both on will give RC3 time), the fourth drive pulse will reset both RC1 and RC2 and turn on RC4, and so on through the read clock cycle. At the completion of each read clock cycle all triggers are reset off.

The oscillator used to drive the clock is normally clamped off until reading is to begin. Because there is no way of knowing just when characters will start being sent from tape, the read clock cycle is not started until the arrival of the first bit of each character read. By starting the read clock with the first bit line, a timing relationship for each character of a record can be realized. The read clock will run through one complete cycle for each character of a record.

The length of the read clock cycle is dependent upon the type of read operation to be performed. The normal read clock cycle is shorter than that of a read check operation. In a normal read operation the clock will run from RC1 time to RC7 time. One output of the RC7 timing circuit is fed through a 400 nanosecond delay line and is then used to trigger a 1000 nanosecond (1 usec) single shot used to reset the read clock triggers. A read check operation runs from RC1 through RC11 time. The extra time required on a read check operation is used as a further check of the data just read.

In a read check operation the read clock timings are slightly different than a normal read. Specifically, RC7 time is actually RC5 time. A write operation control line conditions the RC7 timing circuit to allow an output with the RC1 and RC4 triggers. The reason for this timing change is an added marginal check for the record being read. Also, the RC7 reset line is actually at RC11 time. Again a write operation control line conditions the circuit to obtain the added time.

It is extremely important to realize these variations because the system line names are not so labeled. The RC7 and RC7 reset lines are labeled in the system, but, as mentioned, during a write operation the RC7 time is RC5 and the RC7 reset time is actually RC11. The clock operation otherwise is the same as in a normal read. The RC7 reset line (RC11 when writing) flips a 1000 nanosecond (1 usec) single shot to reset all the read clock triggers at the completion of the read clock cycle.

### 3.4.02 Write Clock

The write clock consists of four binary triggers separated by a 400 nanosecond delay line. The triggers are driven in parallel by a 400 nanosecond timing pulse derived from a crystal oscillator. A control trigger (write condition) comes on early in a write operation and gates oscillator pulses to the clock. The clock operates in a binary fashion similar to the read clock (1 on, 2 on, 1 and 2 on, and so on). After the fifteenth drive pulse the WC1, 2, 4, and 8 triggers will be on. The sixteenth drive pulse resets all the triggers to normal, and one cycle is complete. Since write condition is still on, the oscillator continues driving the clock and another write cycle is started. As long as write condition is on, the clock remains in repetitive cycles. The WC8 trigger also conditions the oscillator drive pulses to insure that the write clock will complete its cycle when write condition goes off.

### 3, 4, 03 Delay Counter

The delay counter consists of nine binary triggers. The DC1 trigger is driven directly from the selected oscillator, forming the drive timing pulse and sample pulse. The next four triggers are driven in parallel by a 400 nanosecond timing pulse, while the next four are driven in series by the output of the previous trigger.

The drive pulses to the clock are conditioned from a speed control circuit. This circuit has either a millisecond control output or a microsecond control output. Since the operation of the counter is so varied, each operation needing the delay counter outputs has a control trigger to start the delay counter at the proper time and in the proper mode. Whenever an operation using the delay counter is complete, the control trigger resets the counter in preparation for the next operation.

The frequency of the drive pulses to the counter is determined by either 729 II or IV operation and the high-low density status.

### 4.0.01 Figure References

Flow Diagrams

To clarify TAU operation, flow diagrams have been included for write, read, read check, backspace, and rewind. The flow diagrams show the word sequence of the way TAU performs an operation, and in no way show how the operations have been performed. With TAU operating correctly, the flow charts tell the sequence of events TAU uses in completing an operation from beginning to end. The diagrams use a 3-block notation. The oval block is used at the beginning to indicate the operation to be performed. It is also used at the end when the operation is complete. The rectangles indicate the event TAU is performing. The diamond blocks are decision blocks with the outputs labeled. The write-up that follows in this section has a brief explanation of each block of the flow diagram.

**Block** Diagrams

Included for read, write, error while writing, and backspace are block diagrams for each of the operations. The block diagrams represent all the necessary timings, conditions, and writing lines TAU uses to perform the operation,

Sequence Charts

A timing sequence chart is also included for read, write, backspace and error conditions while writing. The sequence chart shows the timing relationships for existing conditions of an operation during the operating cycle.

4.1.00 BASIC TAU OPERATIONS

4.1.01 Write Operation

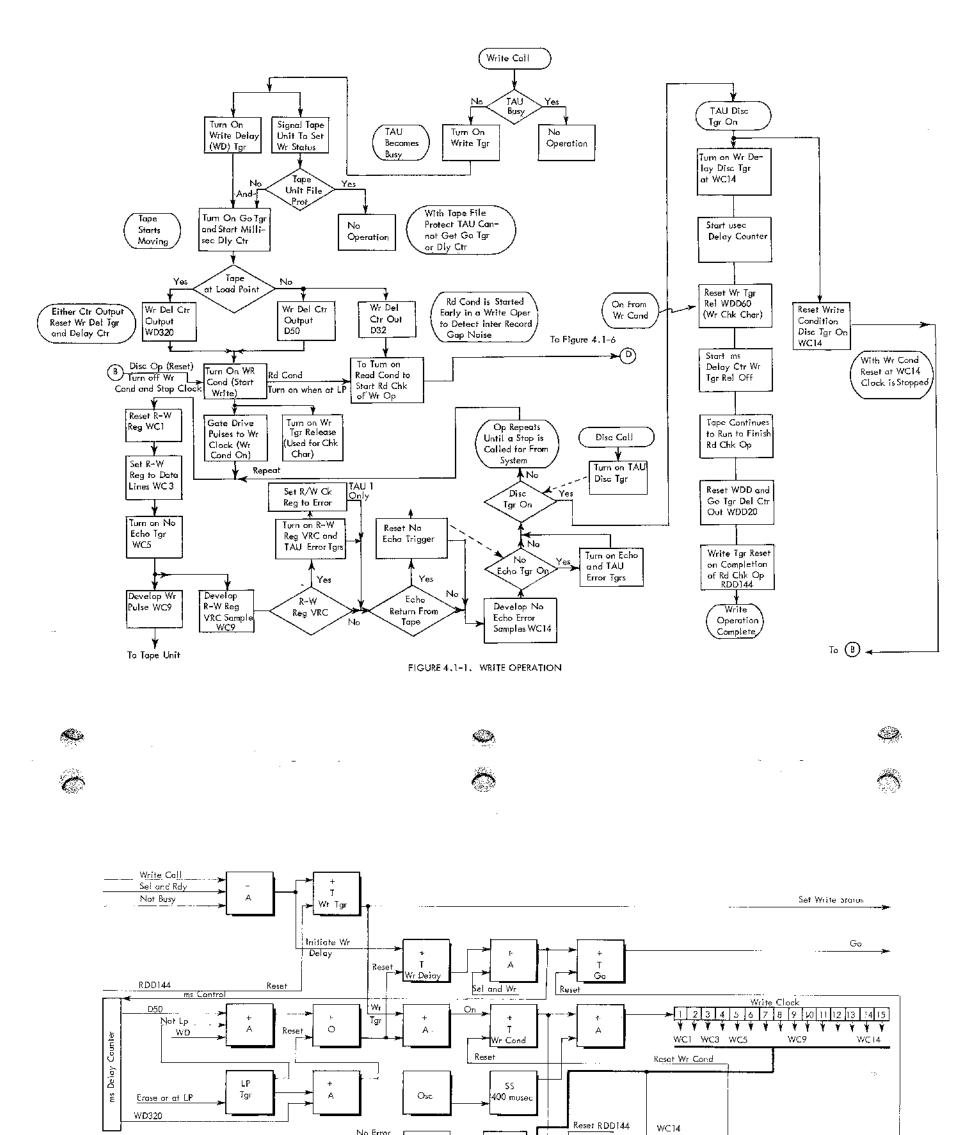

To initiate a write operation, the external system must generate a write call and send it to the TAU. The TAU directly controls all tape movement, develops the write pulses, and controls the data flow from the system through TAU to the tape. The complete write operation of TAU is shown in Figures 4.1-1 through 4.1-5. Following is a brief explanation of each block of the flow diagram.

Write Call

This call is a request signal generated within the external system and sent to the TAU to start the operation.

Busy

If the TAU were performing another operation at the time of the request signal, the busy line would be active and prevent the write call from performing its function. If the TAU were idle, however, the write call signal would initiate action in TAU.

### 4.0.00 INTERNAL OPERATIONS

2

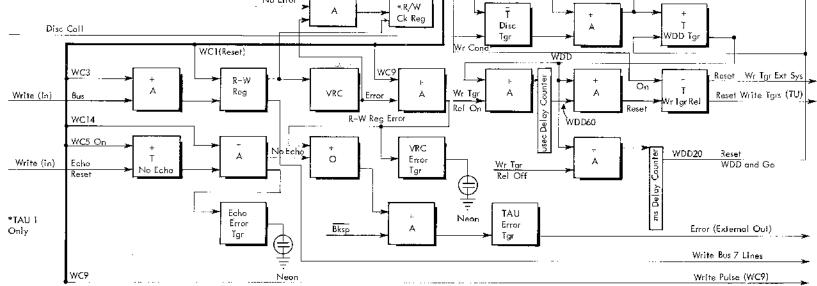

FIGURE 4.1-2. TAU WRITE OPERATION LOGIC

| Starting Tape and Normal Writing (No Errors)      | End of Record Routine (Busy                           |

|---------------------------------------------------|-------------------------------------------------------|

| Write Call                                        | Write Tgr RDD144 Inactive                             |

| Wr Tgr Busy is Active                             | Go WDD20                                              |

| Set Wr Status                                     | Wr Cond WC14                                          |

| Initiate Wr  Def                                  |                                                       |

| Wr Delay Tgr                                      | Wr Clock                                              |

| Go                                                | R-W Reg                                               |

| ms Control                                        |                                                       |

| Delay Ctr D50 (WD320 if at L?)                    | Wr Bus                                                |

| Wr Cond Write Clock Cycle                         | Chk Char<br>Wr Pulse ∏9 ≱Write Point                  |

| Wr Clock 13579 1413579 1413579 1413579 1413579 14 | wrroise                                               |

| R-W Reg3 13 13 13                                 | Disc Tgr RDD144                                       |

| Write Bus Tape                                    |                                                       |

| Wr Pulse99979                                     | WDD Tgr WC14                                          |

| I = Drive Pulse Freq Echo Checking                | used Ctri Gates Used Pulses to Ctr                    |

| No Eche Tgr5                                      | usec Del Ctr                                          |

| Echo from Top <u>e</u> No 🗾 Echo                  | usec Del Ctr Out                                      |

| No Echo Sample 14 14 14                           |                                                       |

| Echo Error Tap <u>e</u>                           | Wr Tr Re] (On with: Wr Cond) <sub>Reset</sub> Wr Tgrs |

| TAU Error Tgr                                     | ( = ···································               |

| VRC Checking                                      | ais CtríGate mis Pulses to Ctr                        |

| Input to VRC                                      | ms Del Ctr                                            |

| VRC Sample                                        | ms Def Ctr Out WDD20                                  |

| VRC Error Tgr                                     | RDD144                                                |

| TAU Error Tgr                                     |                                                       |

×

Ċ

Ŀ,

FIGURE 4.1-3. TAU WRITE OPERATION

C2

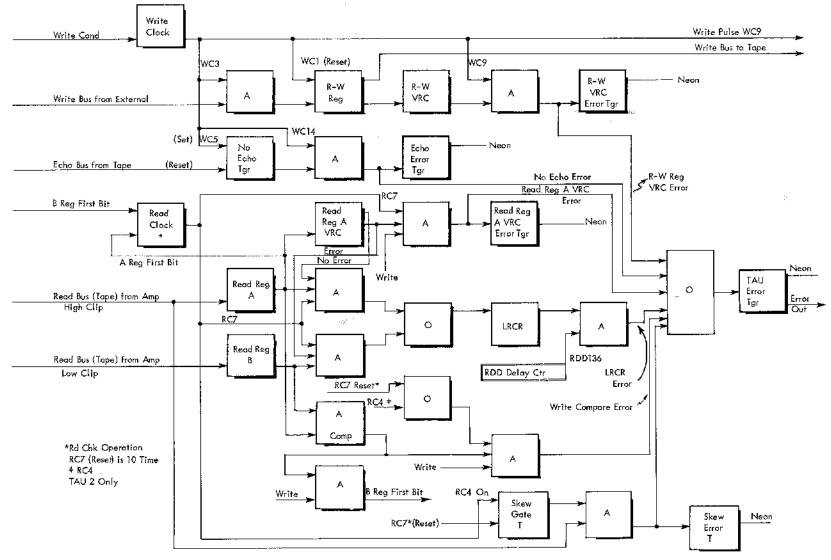

FIGURE 4, 1-4. ERROR CONDITIONS WHEN WRITING

| Conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | <b>Q</b>  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| ee Text}                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |           |

| d Chack While Writing Error Cond<br>* CRese<br>* CRese<br>* CRese<br>* CR Rese<br>* CR | ·<br>·    |

| Write Tgr<br>Read Reg B<br>First Bit<br>First Bit<br>Read Reg B<br>Read Clock<br>Read Clock<br>Read Clock<br>Read Clock<br>Read Clock<br>Red Clock<br>Reg A<br>VRC Sample<br>VRC Sample<br>IAU Error Tgr<br>Comp Sample<br>Comp Sample<br>IRCR Out<br>IAU Error Tgr<br>IRCR Sample<br>IRCR Sample<br>IRCR Sample<br>IRCR Sample<br>Read Read<br>Skew Carte Tgr<br>IAU Error Tgr<br>IAU Error Tgr<br>IAU Error Tgr<br>IRCR Sample<br>IRCR Sample<br>IRCR Sample<br>Skew Carte Tgr<br>Data Line from<br>Final Amp<br>Shaded Area Represents<br>Longer Read Clock Whit<br>Writing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | <b>\$</b> |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |           |

| Writing C         2       3       4       5       6       7         2       3       4       5       6       7         4       5       6       7       7         2       2       3       4       5       6       7         3       4       5       6       7       7         4       5       6       7       7       7         5       6       7       7       7       7         6       8       6       8       8       8       8       8       8       8       8       8       8       8       8       8       8       8       8       8       8       8       8       8       8       8       8       8       8       8       8       8       8       8       8       8       9       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1<                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |           |